技術コラム Column

- si

- 連載コラム :シグナルインテグリティ(SI)改善のポイント

ダンピング抵抗の効果

一般的にドライバICの出力インピーダンスは伝送路の特性インピーダンスに比べて小さいため、ダンピング抵抗が無いと負荷端で大きなリンギングが発生してしまいます。多くの回路設計者はダンピング抵抗の必要性を理解していますが、「ドライバの直近に数10Ω程度の抵抗を入れておいて、基板が仕上がってきたら波形を見ながら調整して定数を決めればいい」程度に考えられている場合が多いのではないでしょうか。然しながら、ダンピング抵抗は回路設計の段階で最適な定数を見積もることが出来ます。今回のコラムでは、ダンピング抵抗の違いによる波形への影響とダンピング抵抗の最適値を見積もる方法を紹介します。

使用する題材について

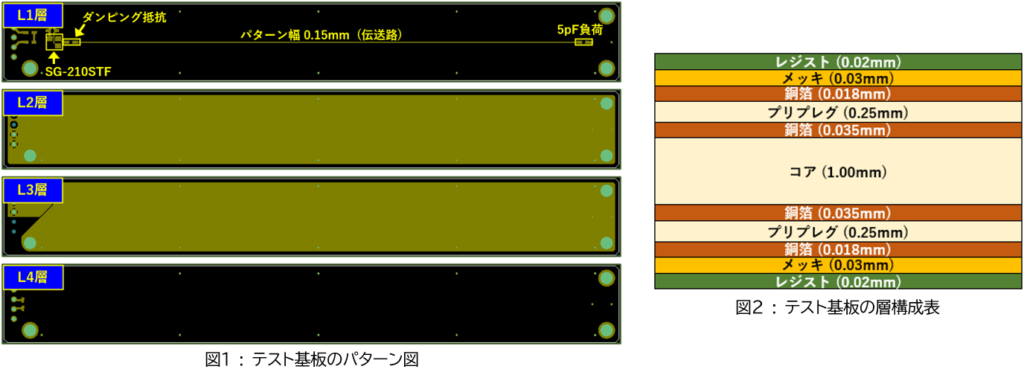

図1のような4層のテスト基板を題材にダンピング抵抗の効果をシミュレーションにより検証してみたいと思います。図2にこの基板の層構成表を示します。L1層(部品面)に伝送路のパターンがあります。L2層にはGNDプレーンがあり、伝送路の基準GNDとしています。部品面(L1層)の左端にセイコーエプソン株式会社様製の水晶発振器 SG-210STFが実装されており、50MHzで発振しています。発振器の出力はダンピング抵抗を通り、伝送路のパターンによって、右端の負荷(5pFのセラミックコンデンサが実装されています)に接続されています。負荷のインピーダンスは高インピーダンスですが、「シグナルインテグリティ(SI)改善のポイント」の第2回のコラムで解説したように、ドライバ側の出力インピーダンスと伝送路の特性インピーダンスが一致していれば、負荷端でのリンギングは発生しないはずです。さて、ダンピング抵抗の定数はどのように決めれば良いのでしょうか。ダンピング抵抗は、上記2つのインピーダンスを一致させるような定数にしなければならないため、まずは、ドライバIC(この例では、SG-210STF)の出力インピーダンスと伝送路の特性インピーダンスを知る必要がありそうです。

ドライバICの出力インピーダンスの見積り

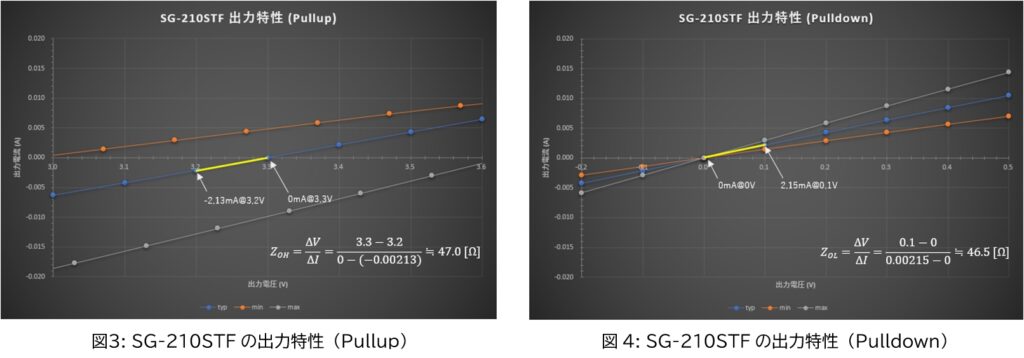

ドライバ側の出力インピーダンスは、ダンピング抵抗がドライバICに十分近ければ、ドライバICの出力インピーダンスとの合成抵抗をドライバ側の出力インピーダンスと見なすことが出来ます。セイコーエプソン株式会社様のサイトを訪れるとSG-210STFのIBISモデルをダウンロードすることが出来ますので、これを利用してドライバICの出力インピーダンスを求めてみます。図3、図4はそれぞれ、サイトよりダウンロードしたSG-210STFのIBISモデルファイルからPullup、Pulldownという項目で得られるデバイスの出力特性をグラフ化したものです。Pullup、Pulldown項目はそれぞれ、High側、Low側の出力特性を担っています。グラフの橙色、青色、灰色はそれぞれTyp値、Min値、Max値を表しています。ここでは、線形性が得られる電源電圧(3.3V)付近(Pullup側)と0V付近(Pulldown側)での傾き(図の黄色部分の傾き)からTyp値を使用して出力インピーダンスを求めます。(※電流の符号は、+側がシンク電流、-側がソース電流を意味します)

インピーダンスZOH、ZOLは、

![]()

となります。

伝送路の特性インピーダンスの見積り

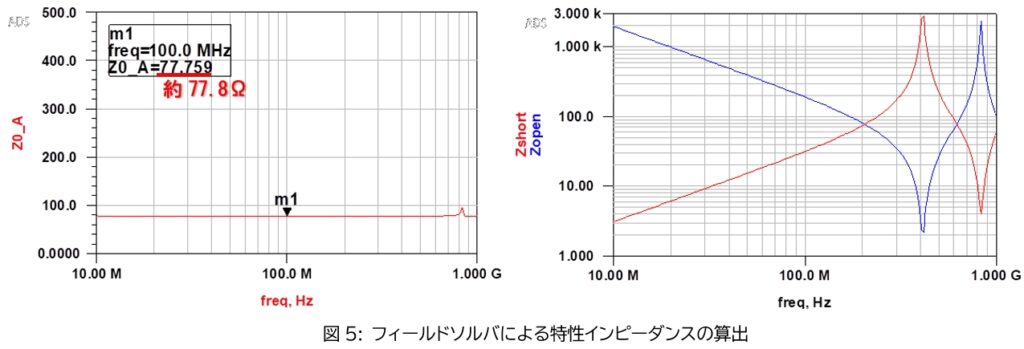

次に、伝送路の特性インピーダンスを求めます。ここでは、Keysight社様のAdvancedDesignSystemのフィールドソルバ(モーメント法)を使用して基板モデルを作成し、算出しています。図5がその結果です。特性インピーダンスは約77.8Ωと求まりました。

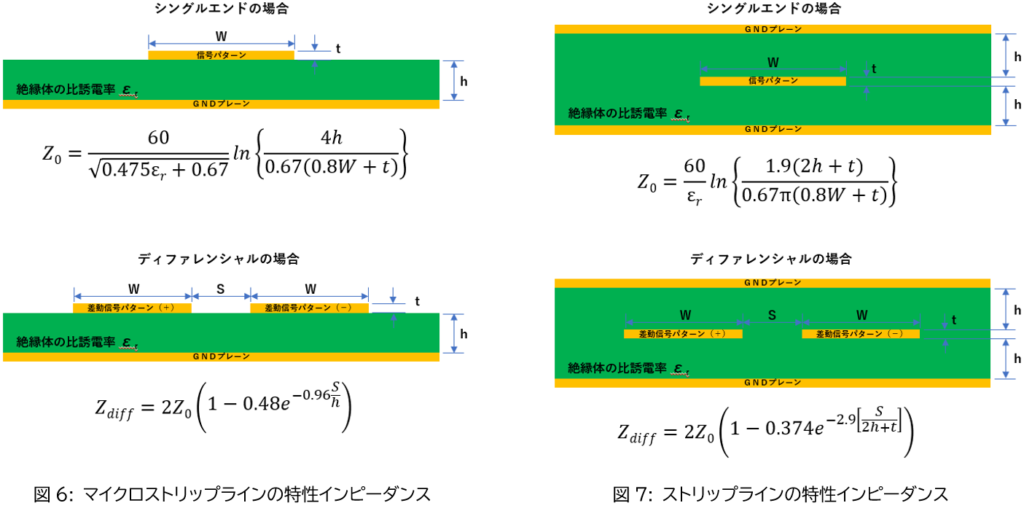

図6、図7はそれぞれ、マイクロストリップライン、ストリップラインの特性インピーダンスを求めるための近似式となっています。フィールドソルバを使用しなくても概略値はこの式から算出出来ますが、レジストが考慮されていない、パラメータの条件によっては精度が悪くなるなど、実際の値から大きく外れている場合もあるため、製作を依頼する基板メーカに問い合わせて確認をするのが確実です。その際には、製作する基板の層構成、使用する基材、信号線のパターン幅(差動信号の場合はライン&スペース)、信号線の配線層とリファレンスGNDとなる層がどの層かといった情報が必要になります。参考までに、図2の層構成表と図6の近似式を使用した伝送路のインピーダンスも求めてみると、

![]()

上式の通り、約80.3Ωとなり、フィールドソルバで求めた値と比べ、2~3Ωのずれがあることがわかります。

ダンピング抵抗値の決定と受信端波形の解析

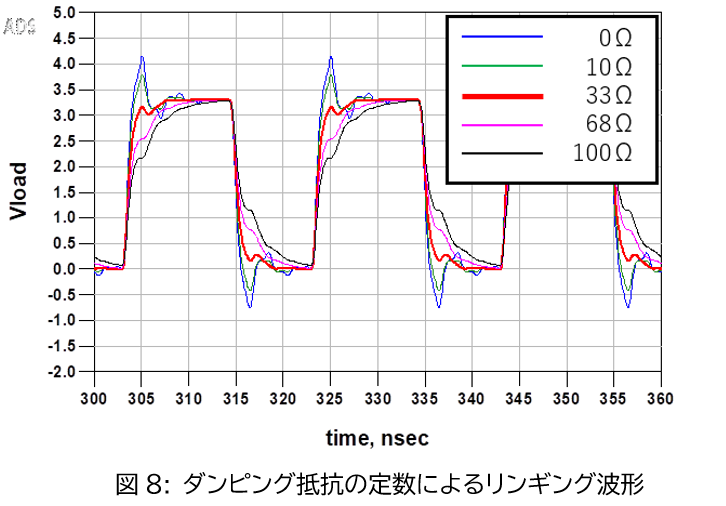

伝送路パターンの特性インピーダンスが77.8Ωであることがわかりましたので、これに合わせるようにダンピング抵抗を決定します。ドライバIC(SG-210STF)の出力インピーダンスが46.5~47Ω(ここでは、46.5Ωとします)なので、その差77.8Ω-46.5Ω=31.3Ωをダンピング抵抗の定数にするのが良さそうです。E12系列の抵抗から、最も近い33Ωをダンピング抵抗として採用することにします。

図8は、ダンピング抵抗を実装した状態で負荷端の波形をシミュレーションで求めた結果です。赤色太線の波形がダンピング抵抗を33Ωとした時の波形で、その他の色の細線の波形は、ダンピング抵抗を0Ω~100Ωまで掃引した時の波形です。ダンピング定数33Ωとした時が最もリンギングが少なく、なまりも無い良好な波形であることが確認出来るかと思います。

ダンピング抵抗の位置による影響

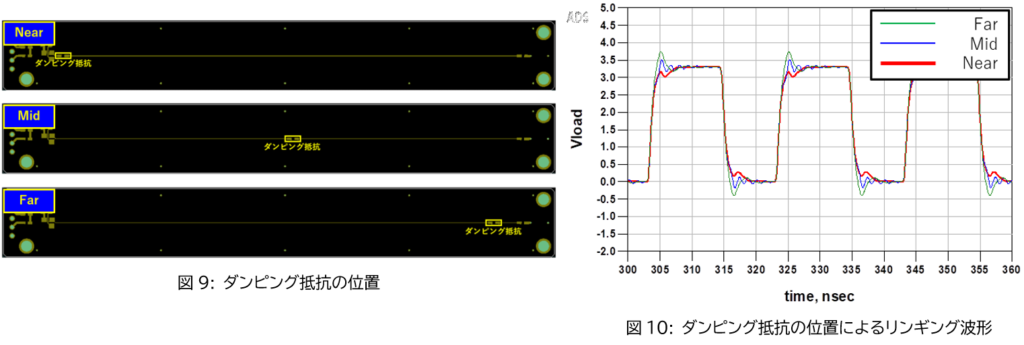

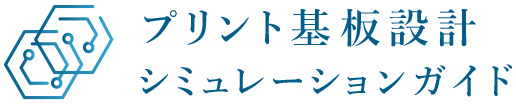

図9はダンピング抵抗の位置をドライバIC直近~再遠端まで修正を加えた配線のパターン図です。「Near」がドライバIC直近、「Mid」がドライバICと負荷端との中間点、「Far」が負荷端直近となっています。

図10はダンピング抵抗33Ωをこれら3種類のパターンに実装した状態で負荷端の波形をシミュレーションで求めた結果です。ドライバIC直近にダンピング抵抗を実装した時の波形が最もリンギングが少なく、ドライバICから離れるほどリンギングが大きくなっていくことが確認出来るかと思います。