技術コラム Column

- si

- 連載コラム :シグナルインテグリティ(SI)改善のポイント

インピーダンス整合(2)

伝送路の途中でインピーダンスが変化する場合

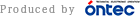

一般的に、伝送路はインピーダンスの変化点が数多くあります。パターン設計の都合で、配線途中にVIAが入ったり配線幅や配線層が変わると各接続点でインピーダンスが変化しますし、送信デバイス~受信デバイス間にプリント基板のパターンのみで結線されない場合も多く、伝送路上にビーズやコンデンサなどの部品を挿入したり、送信デバイスと受信デバイスが別基板で構成され、間にケーブルが入る場合にもインピーダンスが変化します。ここでは、伝送路の途中でインピーダンスの変化が生じる場合を想定してシミュレーションを行ってみます。図2は、信号源インピーダンスを50Ω、伝送路の特性インピーダンスを25Ωとし、伝送路の中間地点から75Ωに変化した場合の例です。(振幅・立上り時間はこれまでと同じです。)

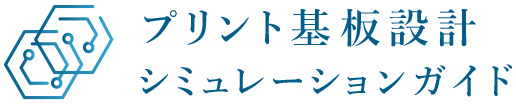

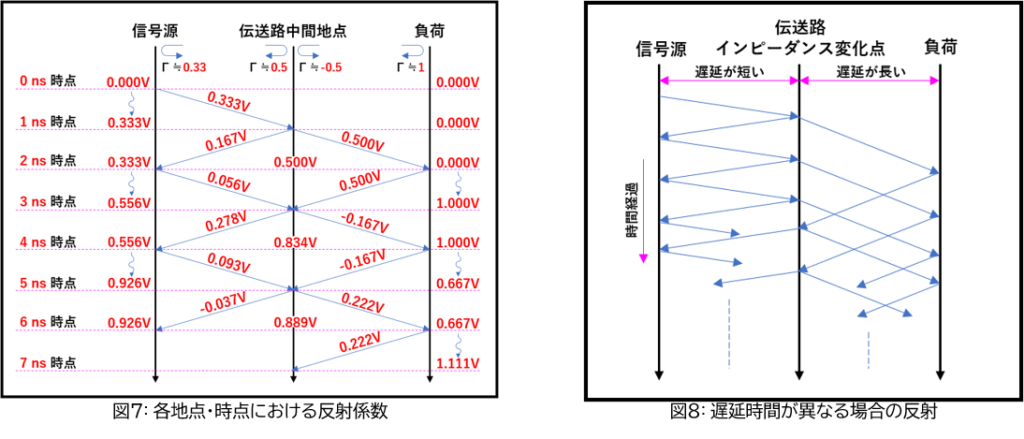

各インピーダンスの変化点における反射係数を予め求めておくと、反射係数はそれぞれ、

伝送路1入力端 ➡ 信号源:0.33

伝送路1出力端 ➡ 伝送路2入力端:0.5

伝送路2入力端 ➡ 伝送路1出力端:-0.5

伝送路2出力端 ➡ 負荷:1

となります。(図1参照)

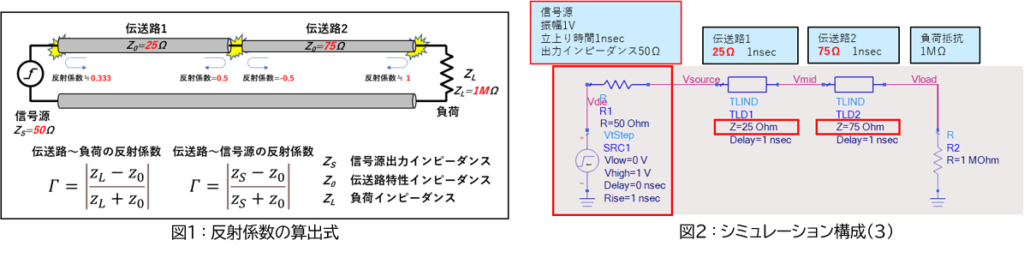

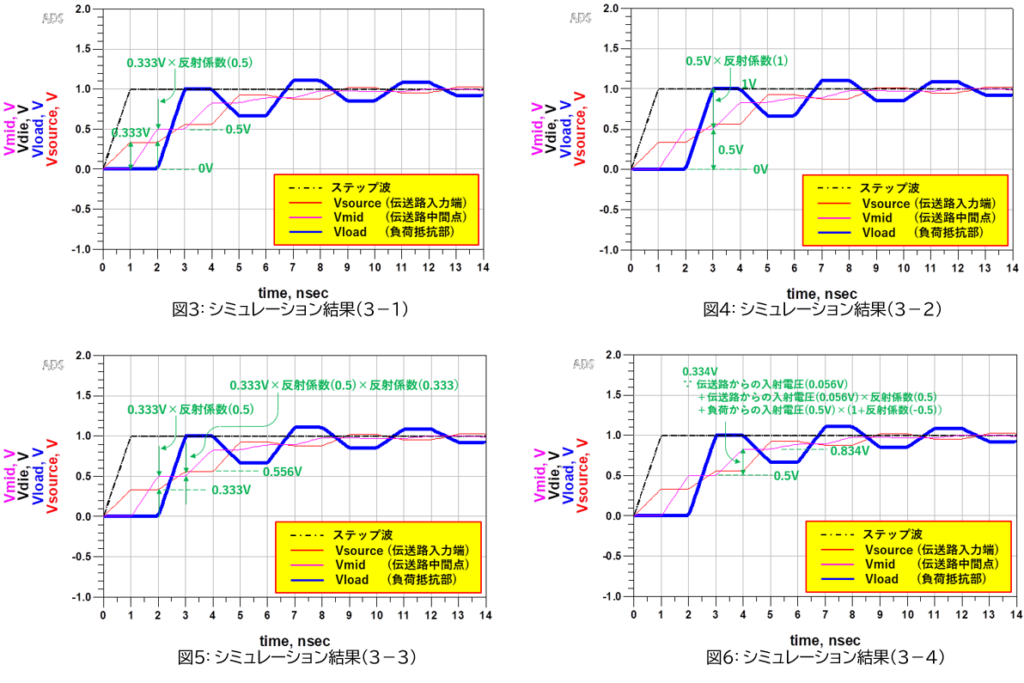

図3は、図2の回路をシミュレーションさせた結果で、図7は、各地点・各時点での入射電圧・反射電圧と、信号源・負荷部での各時点での電圧を図示しています。信号源から発せられたステップ波は、遅延無しで伝送路入力端に到達し、信号源のインピーダンスと伝送路の特性インピーダンスとで分圧され、0.333V(1nsec時点)となっています(赤色波形)。伝送路中間点での反射係数は0.5であるため、2ns時点で0.5Vとなっています(0V+0.333V+0.333V×0.5(反射係数)、(ピンク色波形、図3緑色コメント参照))。負荷から伝送路2への反射係数は1(全反射)であるため、3nsの時点で負荷端で0.5Vの2倍の1V(図4緑色コメント参照)になると同時に、伝送路1から信号源への反射係数は0.333であるため、信号源では0.556Vとなります(0.333V+0.333×0.5(反射係数)+0.333V×0.5(反射係数)×0.333(反射係数)(赤色波形、図5緑色コメント参照))この後の1nsの期間、信号源からの反射波と、負荷からの反射波が、伝送路の中間地点に向かって進み、2つの波は合成されることになります。そのため、4ns時点での伝送路中間点での電圧は、直前の伝送路中間地点の電圧+伝送路からの入射電圧+(伝送路からの入射電圧×反射係数)+負荷からの入射電圧×(1+反射係数)となり、0.834Vとなります(0.5V+0.056V+0.056V×0.5+0.5V×(1+(-0.5))、(ピンク色波形、図6緑色コメント参照))。ここで、(1+反射係数)は、入射電圧に対して透過側に現れる電圧の割合を表しています。これは、透過電圧と反射電圧の和が入射電圧になることを意味します。また、この時の信号源側への反射電圧は、(伝送路からの入射電圧×反射係数)+負荷からの入射電圧×(1+反射係数)で、0.278V、負荷側への反射電圧は、(負荷からの入射電圧×反射係数)+信号源からの入射電圧×(1+反射係数)となり、-0.167Vとなります。これらの反射電圧は、再び信号源や負荷部へ進行・反射し、伝送路中間点に戻ってきます。このような反射を何度も繰り返し、負荷側の電圧は、最終的に信号源の出力インピーダンスと負荷インピーダンスで分圧された電圧(この例では約1V)に収束します。

今回のシミュレーションでは、伝送路1と伝送路2の遅延時間がどちらも1nsでの解析結果でした。遅延時間が異なると、図8で示すように、反射がより複雑になります。冒頭で述べている通り、実際には、インピーダンスの不整合点は様々なところに現れます。これらを十分に考慮して信号品質を評価する必要があることにご注意ください。

信号源インピーダンス=伝送路の特性インピーダンス=負荷インピーダンスの場合

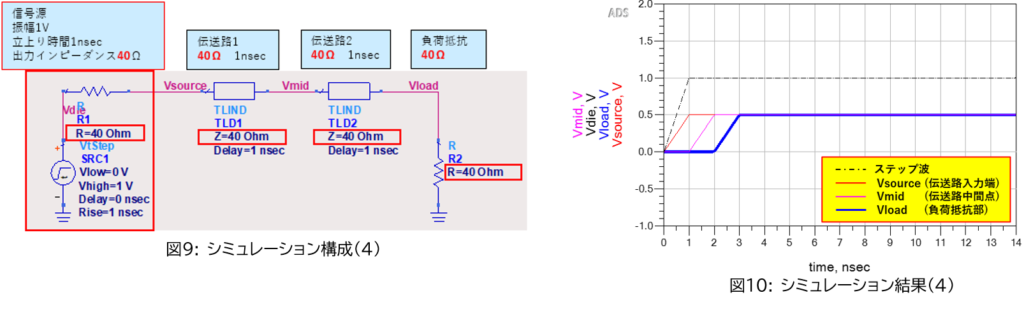

最後に、信号源インピーダンス、伝送路の特性インピーダンス、負荷インピーダンスが全て同じ場合のシミュレーションを行ってみます。

図9は、出力インピーダンス40Ωのステップ波を、 特性インピーダンス40Ωの伝送路と40Ω負荷(終端抵抗)へ励起する回路です。(負荷を40ΩとしているのはDDR3メモリなど高速通信するデバイスの入力インピーダンスを想定しています。一般的に信号源や伝送路に合致させるために負荷側に配置する抵抗を終端抵抗と呼んでいます。 )

図10は、図9の回路をシミュレーションさせた結果です。信号源のインピーダンス、伝送路の特性インピーダンスは共に40Ωであり、インピーダンス整合が取れているため反射はありません(青色波形)。信号源から発せられたステップ波は、遅延無しで伝送路に到達し、信号源のインピーダンスと伝送路の特性インピーダンスとで分圧され、信号源電圧の半分(1ns時点で0.5V)となっています(赤色波形)。ステップ波は、2nsec後(3nsec時点)に40Ωの負荷に到達しますが、伝送路の特性インピーダンス、負荷抵抗は共に40Ωであり、インピーダンス整合が取れているため反射はありません。このため負荷に掛かる電圧は信号源の半分である0.5Vのままで安定します。

この例では、各観測点での反射は一切なく、理想的なインピーダンス整合となっています。受信側デバイスの入力インピーダンスが高いと、伝送路を流れる電流が微小となるため、外来ノイズの影響を受けやすくなります。そのため、高速通信するデバイスにおいては、入力インピーダンスを低くする例が多く見られます。負荷側に電流が多く流れるため電力を多く消費しますが、外来ノイズに強く安定した伝送を行う事が出来ます。これらの構成の注意点としては、負荷側の電圧が信号源の電圧の半分になるということ、また、常時電流が流れるため消費電流が大きくなることです。

SI解析の結果からわかること

これまでの解析結果から、インピーダンスの整合が取れていないと、反射の影響で波形が歪み、オーバーシュートやアンダーシュートにより入力側デバイスに過電圧が掛かったり、閾値を跨ぐリンギングや閾値付近に段付きが発生し、デバイスの故障や伝送エラーの原因となる可能性があることがおわかり頂けるかと思います。また、リンギングの振幅や周波数が高いとEMIノイズの原因にもなるため、この点においても注意が必要です。

理想モデルを通して反射のメカニズムを知ることで、シグナルインテグリティを考慮する必要性があるかどうかを事前に推定することが出来たり、各部の電圧を測定した波形から、何処で反射が起こっているのかを推測しやすくなるのではないかと思います。