技術コラム Column

- pi

- 連載コラム :パワーインテグリティ(PI)改善のポイント

インプットインピーダンス改善の実例

今回のコラムではPDN(電源配線)のインプットインピーダンスを下げるための基本戦略を示した後、簡単な基板をシミュレーションで解析しながらインプットインピーダンスを実際に改善する例を御紹介しようと思います。

PDNのインプットインピーダンス低減のための基本戦略

電源配線にVRMのみが配置されている場合、図1の黒色ラインのようなインピーダンス特性となります。 VRMはDC~数10KHz程度までは低インピーダンスですが、これを超えるとインダクタンス特性となります。 ターゲットインピーダンスを超えないように、通常、赤色ラインのような特性を持つ出力コンデンサ・バルクコンデンサが実装されます。然しながらバルクコンデンサは数100KHz程度まではキャパシタンスとして機能しますが、これを超えるとインダクタンス特性となります。従って、より高い周波数でのインプットインピーダンス低減に効果のあるバイパスコンデンサ(一般的にセラミックコンデンサ)が負荷IC直近に実装されます。これによりピンク色破線のようなターゲットインピーダンスを超えないインプットインピーダンス特性を得ることが出来るようになります。高周波になればなるほど配線インダクタンスの影響を受けやすくなるため、高周波対策用のバイパスコンデンサはICのピン直近に配置する必要があります。

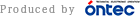

解析する基板パターンと改善方針

図2は、今回解析を行う基板のレイアウトです。8層基板で1層目に電源IC(インダクタ内蔵型)、出力コンデンサ、FPGAが実装されており、8層目にFPGA用バイパスコンデンサが多数配置されています。 解析対象ネットはFPGAのコア電源(VCCINT)で、電源電圧(及び消費電流)は1.2V±3%(4A)で、ターゲットインピーダンスは、18mΩ(FMAX:20MHz)となっています。

シミュレーションでの解析結果を図3に示します。 青色一点鎖線はターゲットインピーダンスで、赤線が解析したインプットインピーダンスです。 第一のピークインピーダンスである27KHz付近及び第二のピークインピーダンスである1.7MHz付近でターゲットインピーダンスを超えているのがわかります。 27KHz付近はPIのインピーダンスとしては比較的低い周波数帯です。 対策としては、電源の過渡応答性の改善、電解コンデンサ・OS-CON・SPCAPなどの容量の大きなバルクコンデンサの使用、パターン幅を太くするなどの対策が考えられますが、今回はバルクコンデンサを使用した対策を行ってみます。 1.7MHz付近はバイパスコンデンサの数や位置の調整、定数の調整などが考えられますが、今回はパターン修正を行わず、コンデンサの定数調整に絞って対策を行っていこうと思います。(OS-CON、SPCAPはパナソニック株式会社様の登録商標です。)

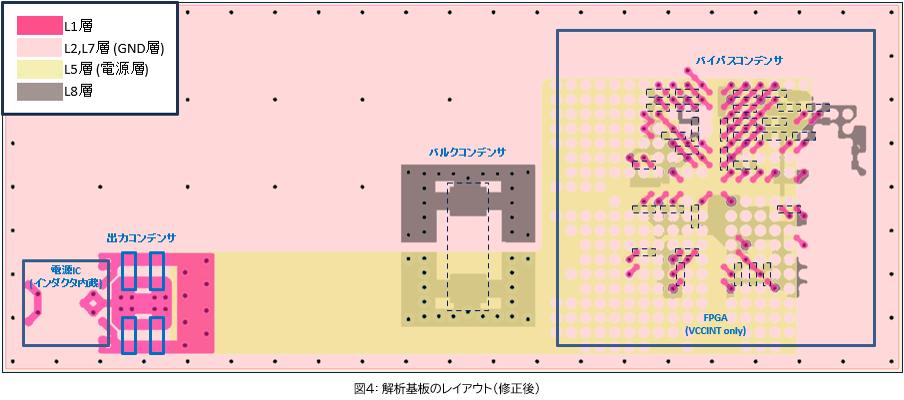

バルクコンデンサによる低周波帯域の改善

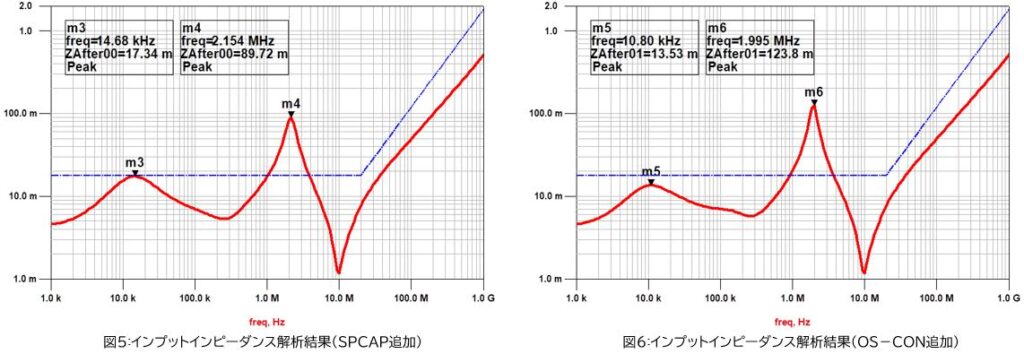

図4は、対策としてFPGA直近にバルクコンデンサとしてSPCAP「EEFCX0D331R」を半田面側(8層)に配置したパターン図で、図5はこれを実装した状態での解析結果です。 この改善により、第一のピークインピーダンスをターゲットインピーダンス以下に抑えることが出来ています。 コンデンサを追加することで、共振点にずれが生じ、ピークインピーダンスの周波数が少しずれています。

次にバルクコンデンサにSPCAPよりも容量の大きなものが選択できるOS-CONを使用してみます。 図6はパナソニック株式会社様製OS-CON「16SEF1000M」にした場合の解析結果です。SPCAP「EEFCX0D331R」と比較すると第一のピークインピーダンスが更に低く抑えられますが、第二のピークインピーダンスは少し高めとなっています。 (そして、やはりピークインピーダンスの周波数は少しずれています。)

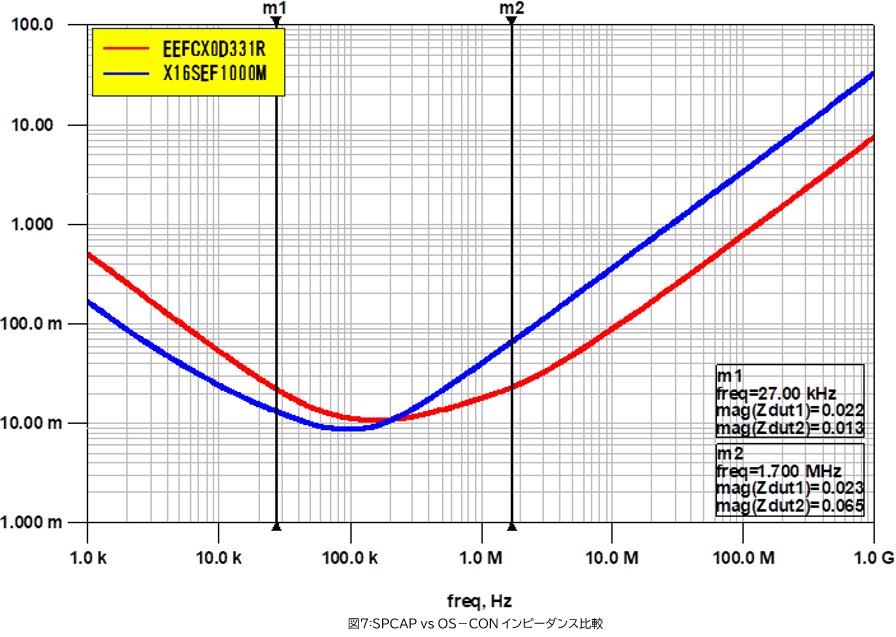

これらの結果は、2つの部品のインピーダンス特性を見ればある程度予想が出来ます。 図7は、SPCAP「EEFCX0D331R」とOS-CON「16SEF1000M」のインピーダンス特性を表したもので、第一のピークインピーダンスである27KHz付近ではOS-CON「16SEF1000M」の方が、第二のピークインピーダンスである1.7MHz付近では、SPCAP「EEFCX0D331R」の方が、インピーダンスが低くなっていることから、これらの結果が順当であることがわかります。

バイパスコンデンサによる高周波帯域の改善

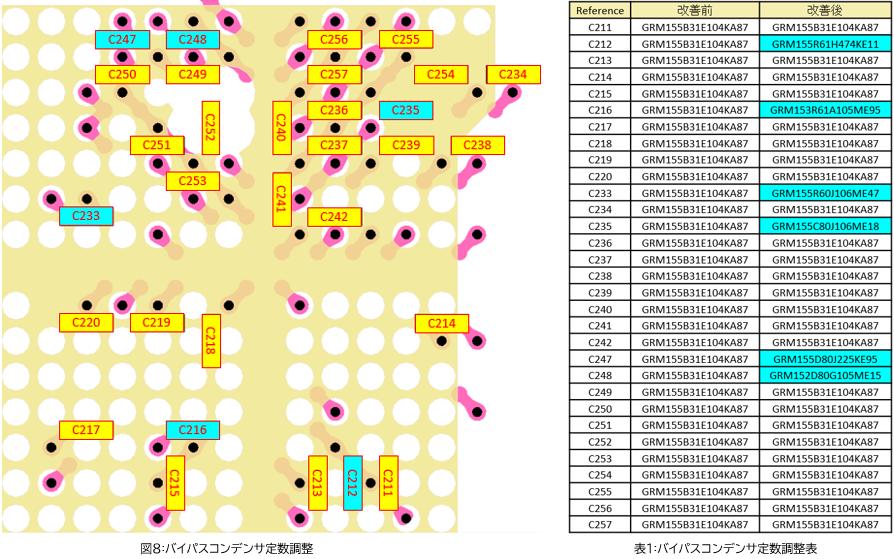

図8は、FPGAのコア電源用バイパスコンデンサの配置を示しています。 この図にはVCCINTボール用のパッド以外は省略されていますが、このFPGAのパッケージはBGA(Ball Grid Array)のため、パッドが格子状に配置され、パッケージ内側には引き出し用のビア以外のスペースはほぼありません。 また、通常、コア電源用ボールは中央に集まっています。 従って、直近にパスコンを配置するには、パッドオンビアを使用するか、この格子の間にビアを配置して、実装面の裏側にパスコンを配置するしかなく、ビアの寄生インダクタンスが必ず付加されることになります。 改善前は0.1μFのコンデンサをボールごとに配置していましたが、インプットインピーダンス低減のために、コンデンサの定数を最適化しました。 図8及び表1の水色の部分が定数変更したコンデンサを表しています。 (これらのコンデンサ部品はすべて村田製作所株式会社様製です。)

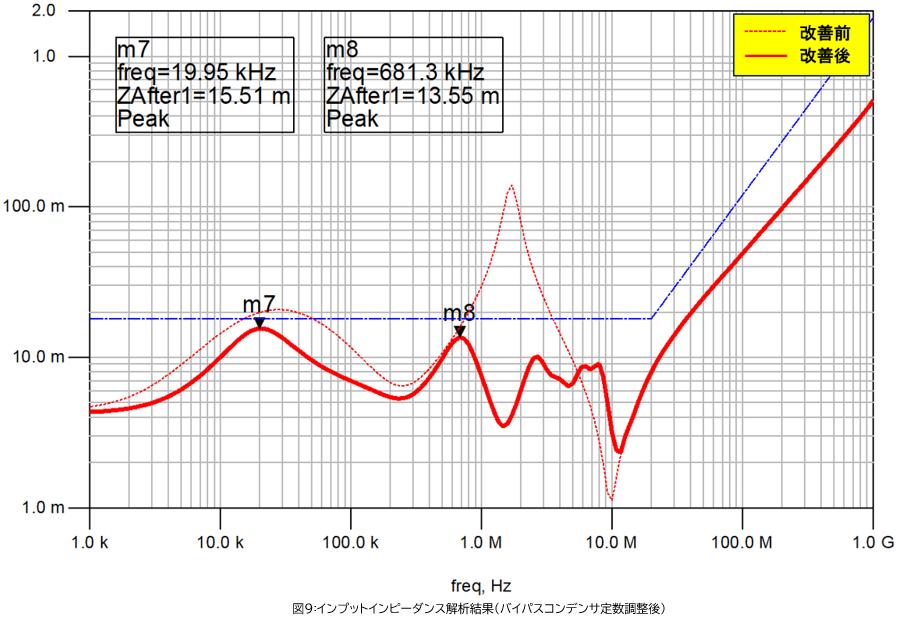

図9はバルクコンデンサの追加とバイパスコンデンサの定数調整後の解析結果です。 全帯域でインプットインピーダンスがターゲットインピーダンスを下回りました。コンデンサは0.1μF~10μFまで容量を少しずつ変えたものを実装することで、各コンデンサが得意とする周波数帯のインピーダンスを下げつつ、反共振を抑えることが出来ています。 反共振(並列共振とも呼ばれます)はインダクタンス成分とキャパシタンス成分が並列に接続されている時に、ある周波数(共振周波数)でインピーダンスが極値を持ってしまう現象です。 ここでは、コンデンサの持つキャパシタンス成分と別のコンデンサが持つ寄生インダクタンス成分との間での並列共振です。 共振点でのインピーダンスは2つのコンデンサの容量が離れている程大きくなる傾向があります。

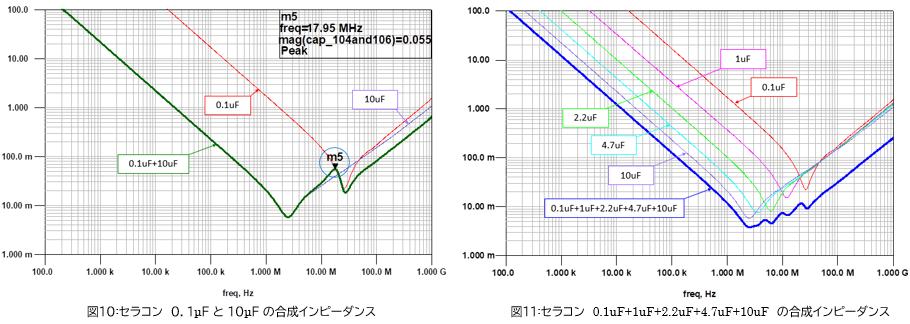

反共振(並列共振)について

図10の緑色太線は0.1μFと10μFのセラミックコンデンサを並列に接続した場合の合成インピーダンスを表しています。 ここでは18MHz付近で反共振が発生しており、合成インピーダンスは0.1 μFのセラミックコンデンサ単体の特性よりも悪化してしまっています。 図11の青色太線は0.1μF、1μF、2.2μF、4.7μF、10μFを並列に接続した場合の合成インピーダンスを表しています。 図10の緑色太線と比べると、反共振が抑えられ良好なインピーダンス特性となっているのがわかります。 図10の緑色太線も図11の青色太線も高い周波数(20MHz~1GHz)でのインピーダンスが低く抑えられているように見えます。 然しながら、コンデンサがプリント基板上に実際に実装された状態では、配線インダクタンスの影響が大きくなり効果が弱くなります。 通常、数十MHzを超えたあたりから、プリント基板上の実装部品でインピーダンスを下げることは難しくなってくるため、オンチップキャパシタなどがその役割を担うことになります。

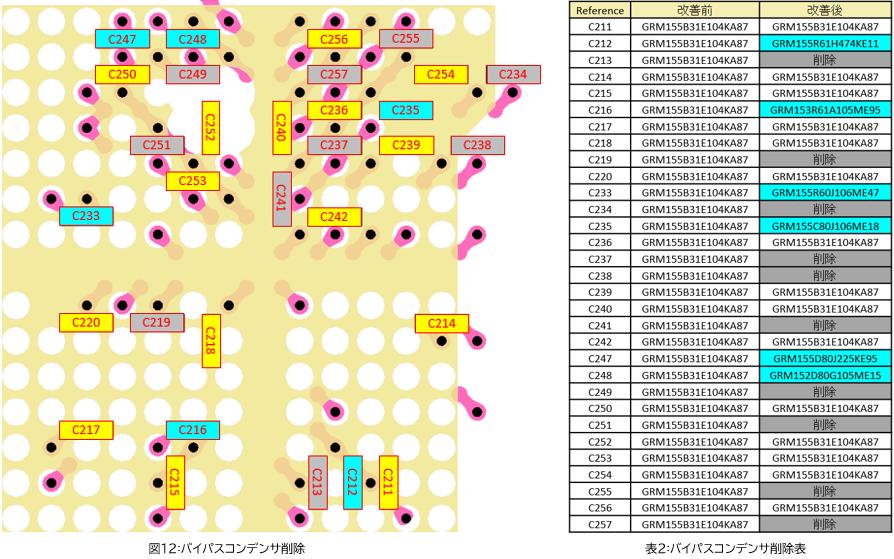

部品削減によるコストカット

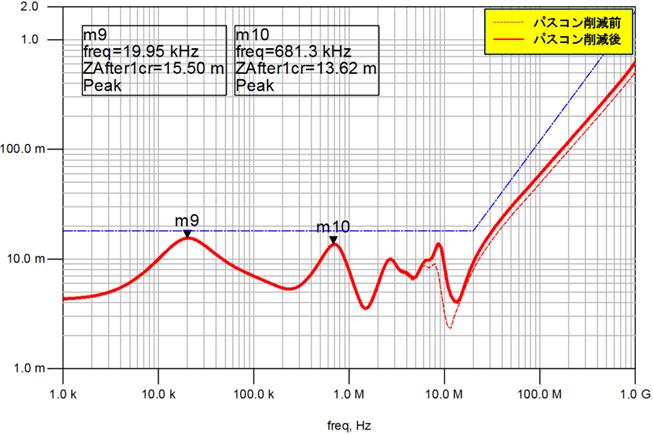

更に、パスコンの数を減らす検討を行います。図9で10MHz以上を確認するとターゲットインピーダンスまで余裕があります。材料費や実装費を削減するため、図12及び表2の灰色の部品を未実装状態にし、複数のボールに対して1個のパスコンを共有しています。

図13はバイパスコンデンサ削減時の解析結果です。 10MHz超えで若干インプットインピーダンスが高くなりますが、それでもまだターゲットインピーダンスまで余裕があります。

最後に

FPGAやSoCなどで、0.8V、1.0Vといった低電圧で動作するICでは、消費電流が大きく、許容電圧範囲も小さくなります。このため必然的にターゲットインピーダンスが低くなりがちで、時には数mΩといったターゲットインピーダンスを満たさなければならない場合もあります。PI解析を行うことで、FPGAやSoCの負荷電流変動時に許容電源電圧変動の規定を満足できるかを検証することができ、これらのICへ電源を安定供給できるようになります。また、ターゲットインピーダンスに余裕があれば、不要な部品を削除してコスト削減するといったことも可能になります。

Intelのサイトではインプットインピーダンスを計算するツールが公開されています。ご興味のある方は、一度ご自身でPDNの設計を実践してみては如何でしょうか。

御参考URL

Intel 電源分配ネットワーク (PDN)