技術コラム Column

- pi

- 連載コラム :パワーインテグリティ(PI)改善のポイント

DC解析によるIRドロップの評価

DC解析の重要性と基板設計の基本戦略

これまで、デジタル回路設計者は、高速信号波形が配線パターンを通ることでどのような波形に変化するかを知るために、基板製作前に検証できるSI解析を重視することはあっても、PI、その中でも最も基本的なDC解析については比較的軽視する傾向にあり、机上計算で簡単に済ませていた場合が多かったと思います。然しながら、近年、電子機器の小型化や高性能化が進み、プリント基板の配線パターンの高密度化に伴いPDN構造が複雑化、更にLSI電源の低電圧化に伴い電源電圧マージンが減少していることにより、より精度の高いDC解析を行う必要性にせまられているかと思います。

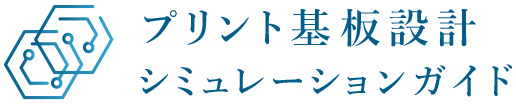

銅配線と言えども電気抵抗を有しており、そこに電流が流れると、多かれ少なかれ必ず電圧降下が発生してしまいます。配線の電気抵抗は、図1で示すように、配線長(L)に比例し銅箔の断面積(t・w)に反比例して大きくなるので、基板設計において電圧降下を抑えるには、配線長を短くするためにVRMを可能な限り負荷の近くに配置すること、また、断面積を確保するために配線幅を太くすることが基本戦略となります。

それでも電源電圧や発熱の要件を満たせない場合は、層数を増やす、厚銅基板を使用する、ジャンパ線やバスバーを使用するといった選択肢を検討していくことになります。配線幅については、1Aあたり1mmという設計ルールが一般的に知られていますが、これは配線の温度上昇を10°C以下に抑えるための基準であり、配線パターンによる電圧降下とは無関係のため注意が必要です。デバイスのピン間からの引き出しや他配線との関係でどうしてもパターン幅が確保できない場合など、やむを得ずパターン幅を細くする必要がある場合は、可能な限りパターン幅の細い区間を短くすることで、この部分での電圧降下を抑えます。細いパターンがあっても、短い区間であれば配線全体の抵抗値に対する影響は少ないため発熱量は低く抑えられます。銅のような熱伝導率の高い材料では、部分的に熱が発生しても、熱伝導により温度の低い部分に熱が簡単に移動しますので、極端な電力差がない限りはそれほど問題にはなりません。

配線パターンの電気抵抗による電圧降下

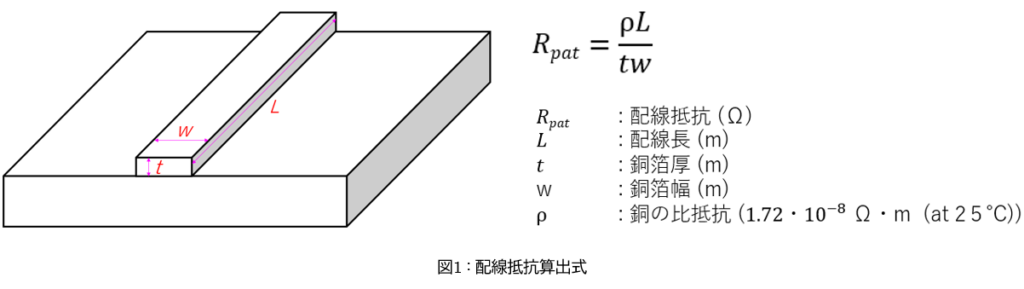

DC解析では、PDNの配線抵抗に加え、コンデンサのESRや、コイル・ビーズの直流抵抗なども考慮して行いますが(DC解析なので、キャパシタンス・インダクタンスは無視されます。)、ここでは配線の分岐やビアの穴など一切無いシンプルな配線パターンの電気抵抗での電圧降下のみを解析ソフトを使用してシミュレーションしてみます。図2はこのシミュレーションの構成図です。配線パターンの左端に1Vの電圧を印加、右端に5Aの電流負荷を接続し、負荷側の電圧を測定しました。銅箔厚(t)は35μm・70μmの2種類、配線幅(w)は1mm・5mm・10mmの3種類、配線長(L)は50mm・100mm・150mm・200mmの4種類にて解析を行いました。図3に、シミュレーション結果のグラフを記載します。配線長が長いほど、また配線幅が細いほど、電気抵抗が大きくなるため、負荷側電圧は低くなっています。

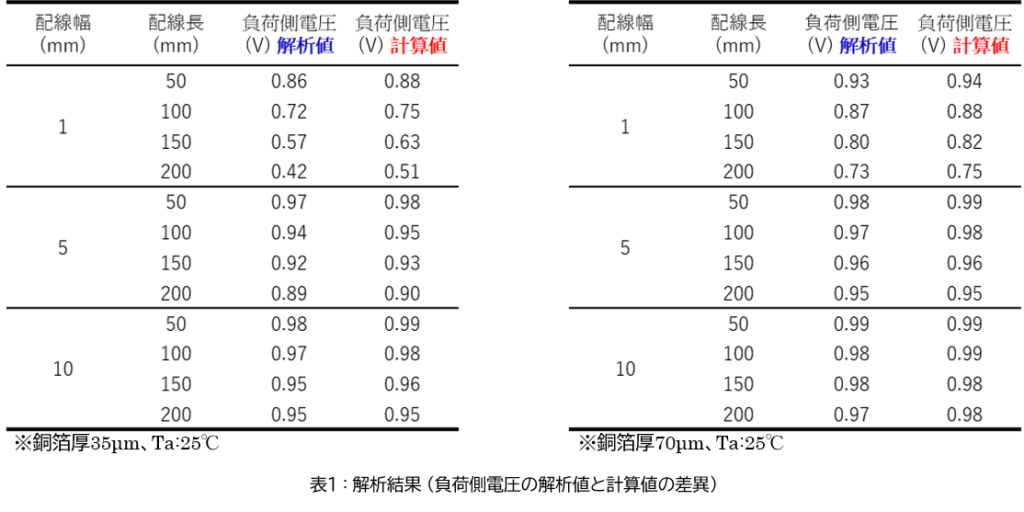

表1は、シミュレーションによる解析値と図1に基づいた計算値を並べたものです。負荷側電圧が低くなるほど、計算値に比べて解析値の方が低くなっているのが読み取れます。

これは、配線パターンのジュール熱による温度上昇に伴って、電気抵抗が大きくなってしまうためです。銅の比抵抗は、下式で示すような温度特性を持っているため、周囲温度や配線パターンの温度が高くなる用途では注意を要します。式から、銅箔の温度が50°C上昇すると1.2倍程度、100°C上昇すると1.4倍程度、抵抗値が上昇することがわかります。

𝜌(𝑇)=1.72×{1+0.00385(𝑇−25)} [μΩcm] ※T: 銅箔の温度

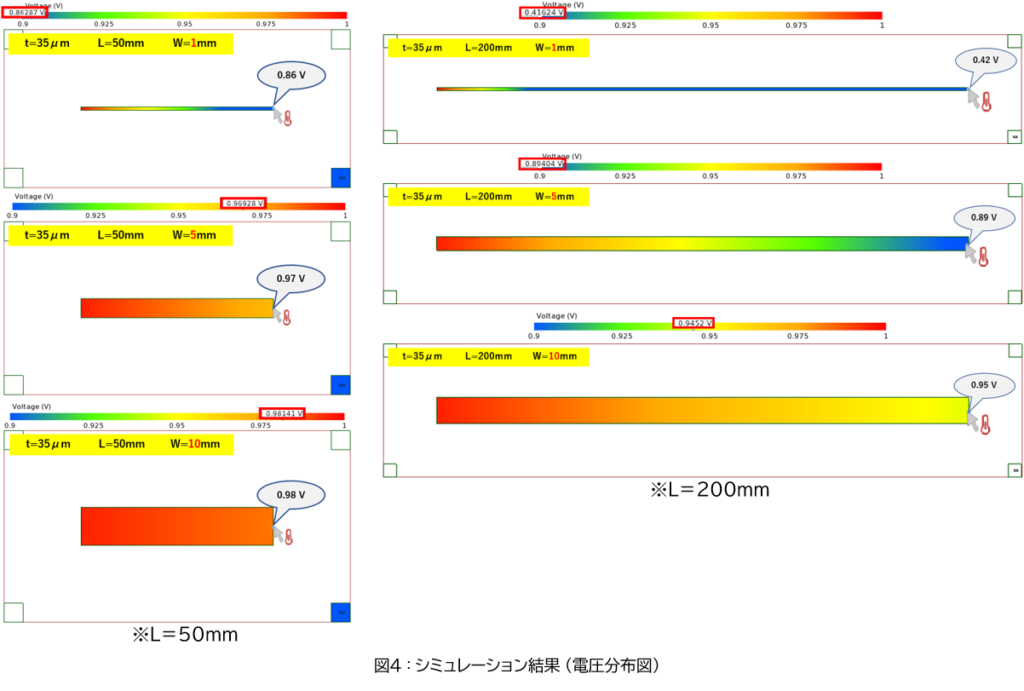

図4は、シミュレーション結果による電圧分布と負荷端での電圧値を表しています。負荷として一般的なFPGAやSoCが接続されている場合を想定し、仮に負荷の電源定格が1V±5%(0.95V~1.05V)であったとすると、配線長(L)=50mmの場合、配線幅(w)=5mm・10mmでは定格を満たしていますが、1mmでは定格を下回っています。配線長(L)=200mmになると、配線幅(w)=1mmに加え5mmの場合でも定格を下回ってしまいます。

ジュール熱による配線パターンの温度上昇

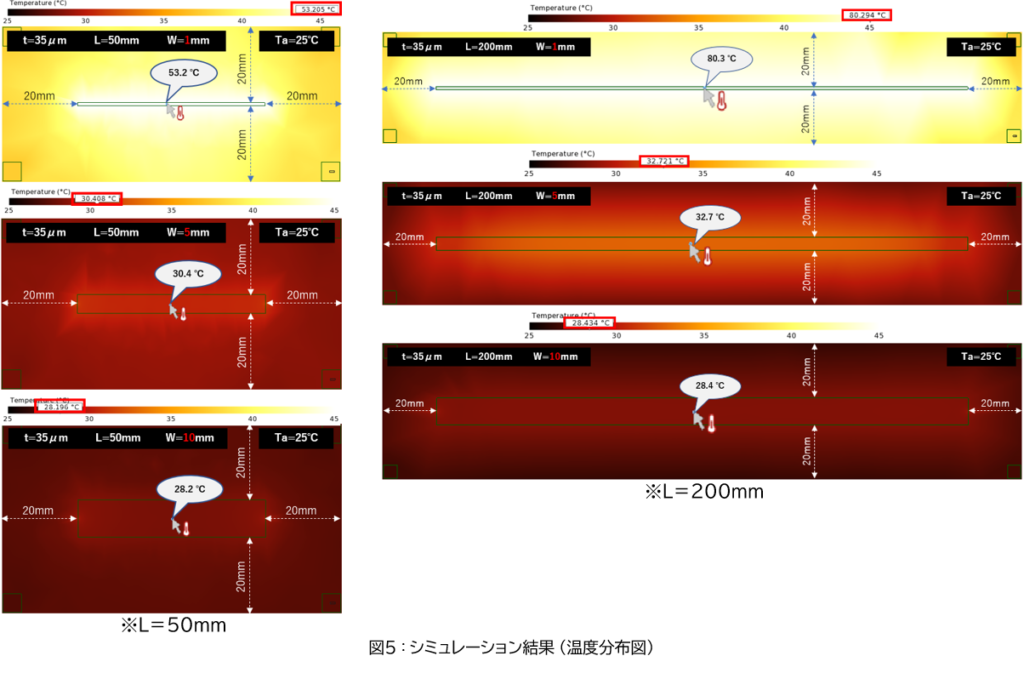

DC解析を行うことで、PDNに流れる電流や、配線抵抗が算出されるため、副次的効果として(こちらが主となる場合もありますが)、PDNの電力損失分布、電流密度分布、温度分布等を得ることが出来ます。先ほど説明した銅箔の抵抗の温度係数を考慮に入れた電気-熱連成解析により、配線や部品の温度上昇を含めた電圧降下を求めるといったことが可能となります。図5は、それぞれ、先程のシミュレーション結果から、配線パターンと基材各部の温度分布を解析したものです。配線の温度上昇を10°C以下に抑えるための基準として、配線幅を1Aあたり1mm以上にするという設計ルールが妥当であることがわかります。

配線層切り替えビアの数とビア径について

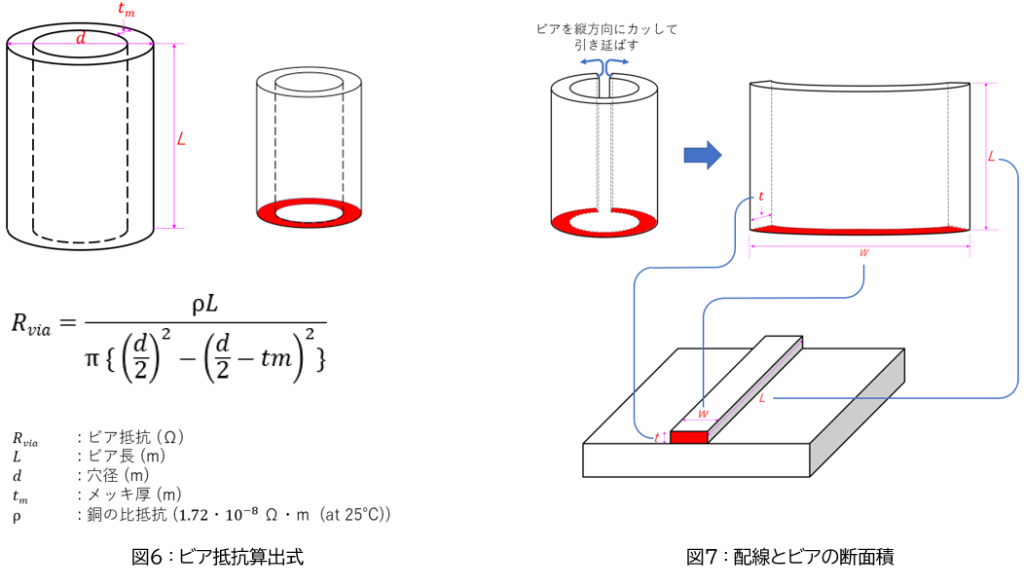

ビアも銅配線の一部であり電気抵抗が存在します。ビアの電気抵抗は図6に表す式にて算出することが出来ます。図の赤色部分は配線抵抗算出式における断面積(t・w)、ビア長(高さ)が同じく配線長(L)に相当します。右辺の分母は図の赤色部分の面積を求めているだけで、基本的には配線抵抗と同じで長さに比例し断面積に反比例します。ビアを図7のように縦方向にカットして引き延ばすと、配線抵抗の算出と同じであることが直観的に理解できるかと思います。

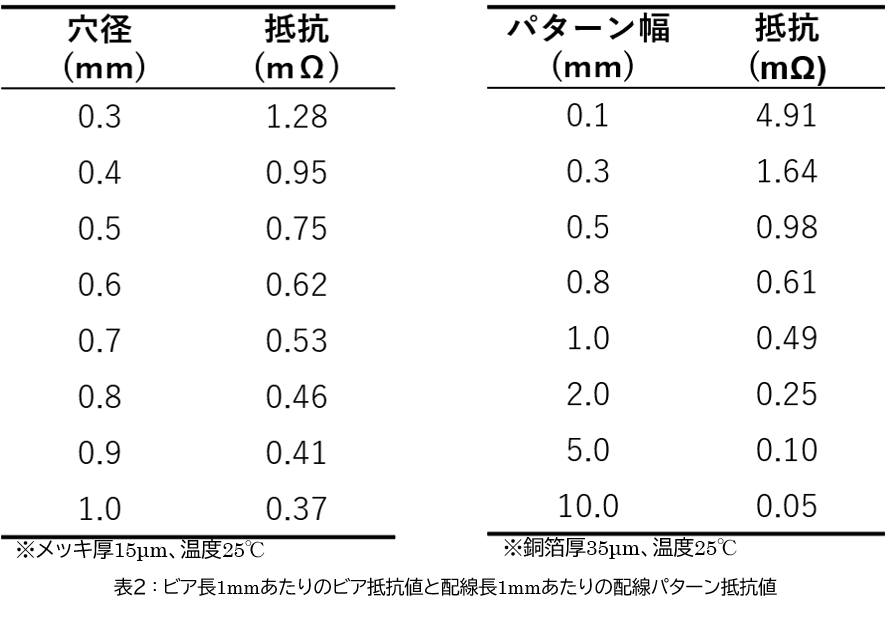

配線層を移動する際の必要なビア数やビア径についてですが、基本的にはビアの合成抵抗を配線と同等にすれば、ビアも配線の延長(ビア長だけ配線が伸びた)と考えることが出来るかと思います。表2の左側は、メッキ厚15μm・温度25°Cにおけるビア長1mmあたりのビア抵抗値、右側は、銅箔厚35μm・温度25°Cにおける配線長1mmあたりの配線パターンの抵抗値を示しています。単位長あたりの抵抗値を配線とビアとで同等にするためには、例えば、5mm幅のパターンに対して、穴径0.3μmのビアの場合で13個(1.28÷0.10=12.8)、穴径0.6μmのビアで7個(0.62÷0.10=6.2)設ければ良いことがわかります。ただ、このような計算に基づいて求められたビアの数やビア径は、実際には過剰品質となる場合が殆どです。

配線抵抗の時にも述べましたが、ビアの長さは長くても基板厚まで(一般的なプリント基板であれば1.6mmまで)です。従って、配線全体の長さに比べてビアの長さの割合は低く、やはり配線全体の抵抗値に対する影響は少ないものと考えられます。仮にビアの数が足りず、接続される配線パターンよりも少し抵抗値が大きくなり、部分的に熱が多く発生したとしても、ビアに接続されている配線が放熱板となって、温度の低い配線パターンの方へ熱が簡単に移動します。限られたスペースの中で不必要にビアの数を増やしたり、ビア径を大きくしないため、シミュレーションツールを活用してビアを最適化することが好ましいと思います。