技術コラム Column

- si

- 連載コラム :シグナルインテグリティ(SI)改善のポイント

インピーダンス整合(1)

インピーダンス整合とは?

インピーダンス整合とは、信号を出力するデバイスの出力インピーダンス、伝送路の特性インピーダンス、伝送路中の部品やそのパッドのインピーダンス、信号を受信するデバイスの入力インピーダンス等を整合させることで、インピーダンスマッチングとも呼ばれます。インピーダンスの整合が取れていないと、その部分で反射が発生します。プリント基板上において、低速で動作する回路では、これらの反射は問題になりませんが、数10MHz~数100MHzを超える信号では、反射による波形の歪が無視できなくなり、デバイスの故障や伝送エラーの原因となる場合があります。

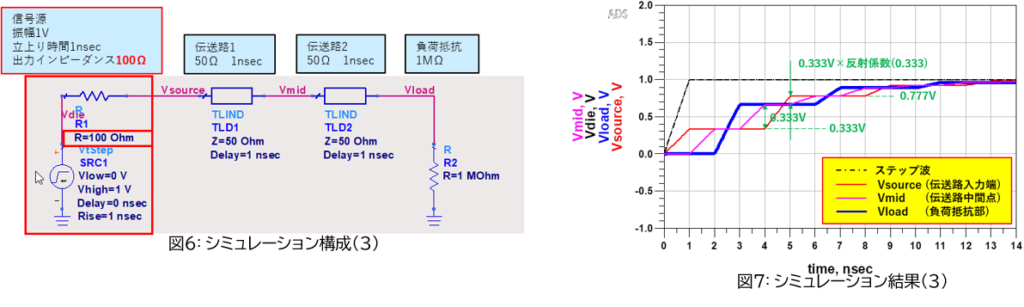

反射係数について

反射係数 Γ は、伝送路や回路部品などの接続部における入射波と反射波の割合を表しています(図1参照) 。反射係数は0~±1の値を取り、0は無反射、1は全反射を表します。符号がマイナスとなる場合は、入射波と反射波の位相が反転します。反射の過程で周波数が変化することはありません。図1において、伝送路の特性インピーダンス 𝑍₀ と負荷インピーダンス 𝑍L の反射係数は、𝛤=|(𝑍L−𝑍₀ )/(𝑍L+𝑍₀ )|のようになります。例えば、伝送路の特性インピーダンスが50Ωで、負荷インピーダンスが100Ωの場合、反射係数Γ=0.333となり、入射波の33.3%が反射します。負荷インピーダンスを50Ωにすると、反射係数Γ=0となり、反射は発生しません。また負荷インピーダンスをハイインピーダンスにすると、反射係数Γ≒1となるため、入射波の全てが反射します。他にも信号反射を表す指標として、SパラメータにおけるS11(リターンロス)やVSWRなどがありますが、本質的には同じものです。

インピーダンス不整合時の波形がどのようになるのかを理解しやすくするため、ここからしばらくの間、理想モデルでの解析結果と反射のメカニズムについて触れていきたいと思います。

インピーダンス整合されている場合

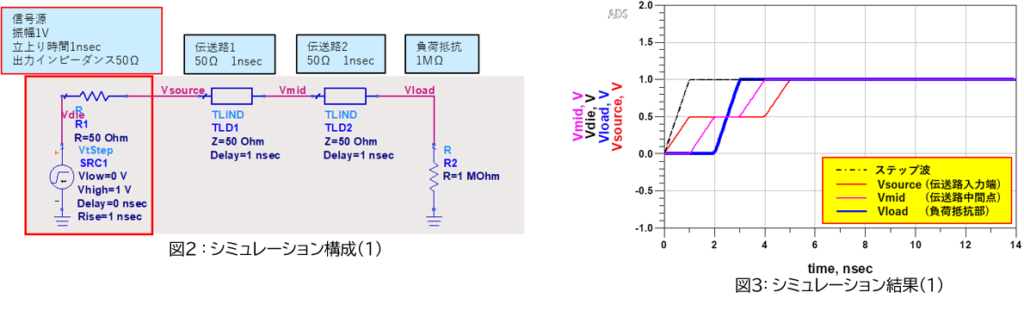

図2は、信号源が、振幅1V、立上り時間1nsec、出力インピーダンス50Ωのステップ波を、 特性インピーダンス50Ωの伝送路と1MΩの負荷へ励起する回路です。伝送路途中の波形を観測するために、便宜上、伝送路は伝送路1と伝送路2の2つに分けています。(負荷を1MΩとしているのは、一般的なCMOSデバイスの入力インピーダンスがハイインピーダンスであるためです。)

図3は、図2の回路をシミュレーションさせた結果です。信号源のインピーダンス、伝送路の特性インピーダンスは共に50Ωであり、インピーダンス整合が取れているため、負荷抵抗部での反射はありません(青色波形)。信号源から発せられたステップ波は、遅延無しで伝送路入力端に到達し(本来はこの間にも半導体内のワイヤ、リード線などの非常に短い伝送路がありますが、ここでは無視しています)、信号源のインピーダンスと伝送路の特性インピーダンスとで分圧され、信号源電圧の半分(1nsec時点で0.5V)となっています(赤色波形)。伝送路の特性インピーダンスは一定であるため、伝送路中間点での波形の変化は無く、伝送路入力端と同じ波形が1nsec遅れで観測されています(ピンク色波形)。ステップ波は、2nsec時点で1MΩの負荷に到達しますが、負荷抵抗がハイインピーダンスで反射係数が1であるため、全反射し、1ns後の3ns時点で0.5Vの倍の1Vとなっています(青色波形) 。この反射波は、伝送線路を介して信号源に戻って行きますが、伝送路の特性インピーダンスと信号源はインピーダンスが整合しているため、更なる反射は発生しません。このため負荷に掛かる電圧は1Vのまま安定状態となります。

信号源インピーダンス<伝送路インピーダンスの場合

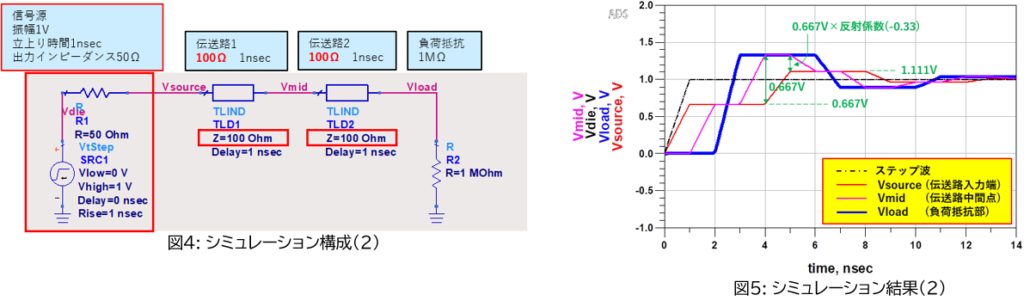

図4は、図2から伝送路の特性インピーダンスを100Ωに変更した回路です。

図5は、図4の回路をシミュレーションさせた結果です。信号源のインピーダンスは50Ω、伝送路の特性インピーダンスは100Ωなので、インピーダンス整合が取れておらず、負荷抵抗部での反射が見受けられます(青色波形)。信号源から発せられたステップ波は、遅延無しで伝送路入力端に到達し、信号源のインピーダンスと伝送路の特性インピーダンスとで分圧され、0.667V(1nsec時点)となっています(赤色波形)。伝送路の特性インピーダンスは一定であるため、伝送路中間点での波形の変化は無く、伝送路入力端と同じ波形が1nsec遅れで観測されています(ピンク色波形)。ステップ波は、2nsec時点で1MΩの負荷に到達しますが、負荷抵抗がハイインピーダンスで反射係数が1であるため、全反射し、1ns後の3ns時点で0.667Vの倍の1.333Vとなっています(青色波形)。この反射波は、同時に、伝送線路を介して信号源に戻って行き、3ns時点で伝送路中間点に到達し、更に1ns後の4ns時点で1Vとなります(ピンク色波形)。そして、同時点で信号源(伝送路入力端)に到達しますが、インピーダンス不整合のため、ここで再び反射が発生します。反射係数は-0.333であるため、1ns後の5ns時点で、約1.111Vになっています(0.667V+0.667V+0.667×(-0.333)(反射係数)、緑色コメント参照)。このように反射波は信号源と負荷との間を行き来するため、オーバーシュート(ステップ波が立下りエッジの場合はアンダーシュート)やリンギングが発生することになります。

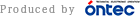

信号源インピーダンス>伝送路インピーダンスの場合

逆に、信号源インピーダンスの方が伝送路インピーダンスより高い場合はどうなるでしょうか。図6は、出力インピーダンス100Ωのステップ波を、 特性インピーダンス50Ωの伝送路と1MΩの負荷へ励起する回路です。

図7は、図6の回路をシミュレーションさせた結果です。信号源のインピーダンスは100Ω、伝送路の特性インピーダンスは50Ωなので、インピーダンス整合が取れておらず、負荷抵抗部での反射が見受けられますが、「信号源インピーダンス<伝送路インピーダンスの場合」とは様子が異なります(青色波形)。信号源から発せられたステップ波は、遅延無しで伝送路入力端に到達し、信号源のインピーダンスと伝送路の特性インピーダンスとで分圧され、0.333V(1nsec時点)となっています(赤色波形)。伝送路の特性インピーダンスは一定であるため、伝送路中間点での波形の変化は無く、伝送路入力端と同じ波形が1nsec遅れで観測されています(ピンク色波形)。ステップ波は、2nsec時点で1MΩの負荷に到達しますが、負荷抵抗がハイインピーダンスで反射係数が1であるため、全反射し、 1ns後の3ns時点では、0.333Vの倍の0.666Vとなっています(青色波形)。この反射波は、同時に、伝送線路を介して信号源に戻って行き、3ns時点で伝送路中間点に到達し、更に1ns後の4ns時点で0.666Vとなります(ピンク色波形) 。そして、同時点で信号源(伝送路入力端)に到達しますが、インピーダンス不整合のため、ここで再び反射が発生します。反射係数は0.333であるため、1ns後の5ns時点で、約0.777Vになっています(0.333V+0.333V+0.333V×0.333(反射係数)、緑色コメント参照)。このように反射波は信号源と負荷との間を行き来するため、立上りや立下り波形に段差が生じることになります。受信デバイスのスレッショルド電圧付近で、CLK信号に対してこのような段差が生じると、ダブルクロッキングが発生したり、セットアップ/ホールド時間規定のマージンを減少させる原因となるため、特に注意を要します。