技術コラム Column

- si

- 連載コラム :シグナルインテグリティ(SI)改善のポイント

シグナルインテグリティ(SI)とは?

シグナルインテグリティ(SI)とは?

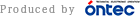

シグナルインテグリティ(またはSI)は、電気信号の品質または、電気信号の品質を測定する尺度のことで、多くの場合、信号の電圧波形で表されます。シグナルインテグリティの評価は高速デジタル信号(プリント基板においては、およそ数10MHz以上)において行うことが多いですが、アナログ信号の場合や、低速信号であっても伝送距離が長い場合には、その評価が必要になる場合もあります。デジタル信号とは言え、全ての信号は基本的にアナログであり、ノイズ、歪、損失などにより、理想的なパルス波形にはなりません。シグナルインテグリティを保証する、つまり信号品質が規定値を満足していることを検証するにはシミュレーション技術が不可欠です。図1のような、アイマスク規定、オーバー/アンダーシュート規定などに準拠しているかが主な基準となります。

過去の苦い経験から

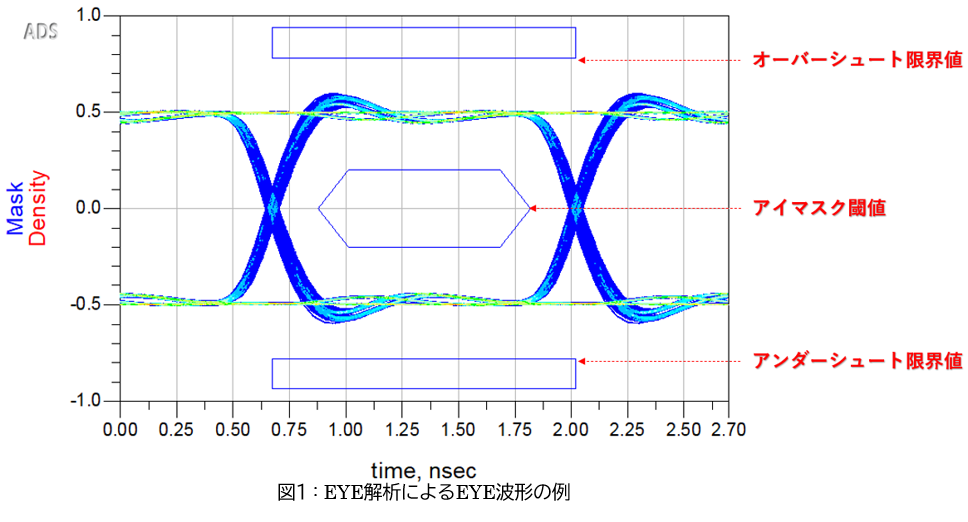

私が過去OEM製品の設計・開発に携わっていた頃、物流倉庫現場へのシステム納品時にトラブルを起こしたことがありました。図2で示すように、中央に操作端末と、十数か所あるバースの搬入用コンベアを制御する制御端末が各バースに設置され、操作端末と全ての制御端末は3Mbpsでマルチポイント半二重非同期シリアル通信を行っていました。これらは図2のような配線トポロジーで接続工事を行い、いよいよ稼働試験となりました。然しながら、稼働試験では通信エラーが頻発し全く動作しません。各端末の受信端の通信波形を確認したところ、もはや波形が歪んでいるというレベルではなく、原型パルス波形の名残が確認出来ないほど酷い状態となっていました。

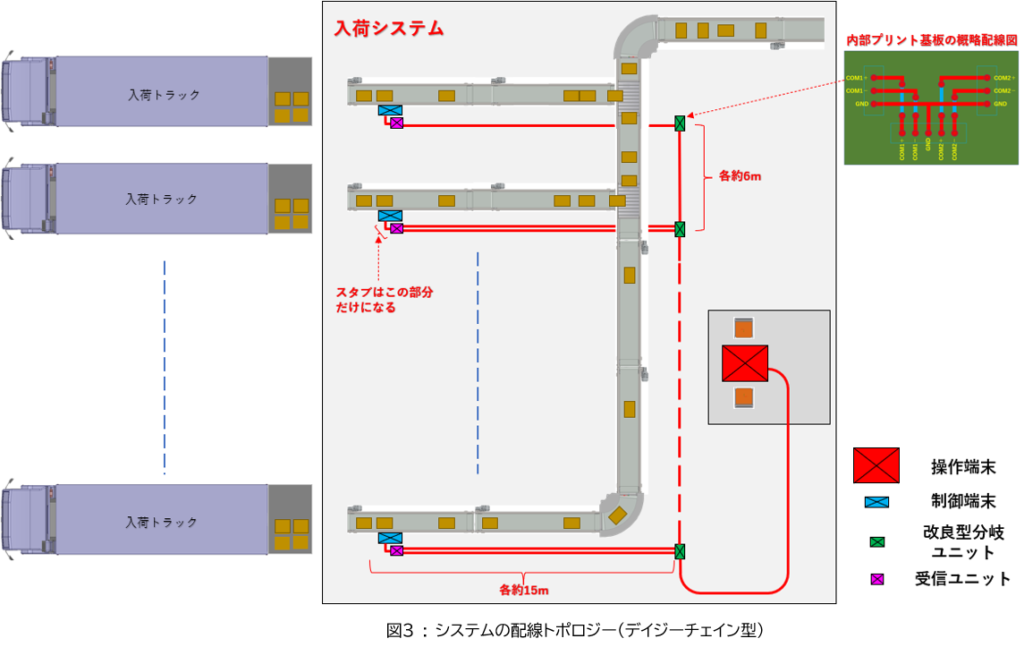

結局のところ、今から考えると当然なのですが、配線トポロジーがT字配線であったことに起因する反射が原因であることがわかり、顧客の要求である「1台の制御端末が故障した場合に通信経路への影響を無くす」ことも考慮し、急遽、図3のように、T分岐ユニットを改良型に変更、受信ユニットを新たに作成し、トポロジーをデイジーチェーン(一筆書き配線)に変更することで事なきを得ました。

こういった苦い経験から低速通信であっても配線長が長くなると、信号反射の影響が無視出来ないことを再認識させられました。当時はまだシグナルインテグリティという言葉もそれほど普及しておらず、数10MHzの信号が高速と言われていた時代でしたが、ここ20年程のテクノロジーの進化で、昨今では数GHz~数10GHzが当たり前の時代になり、プリント基板上の数mm程度の配線においても、信号の反射に最大限の配慮を行う必要が生じています。

このシステムでのビットレートは3Mbpsでしたが、仮に1000倍の3Gbpsになると、数メートルのケーブルによるスタブで発生していた現象が、プリント基板上のミリメートルオーダのスタブ配線でも発生することになります。つまり、プリント基板上の配線は、このシステム図で示したケーブル配線の縮図と考えることが出来ます。今後も引き続きデジタル信号の高速化に対する需要は高まって行くと思われます。シグナルインテグリティの保証に対する需要が増し、デバイスメーカーでは、ガイドラインなどを作成して対応しています。またセットメーカーにおいては、基板製造前にシミュレーション技術を用いて波形を確認し、シグナルインテグリティに対する裏付けを行う設計者が増えてきています。

どのような場合に解析が必要か?

先程の例で示しましたように、「低速信号だからシグナルインテグリティを考慮する必要は無い」という結論を出すことは早計です。デジタル信号において、電気長の往復時間が立ち上がり時間よりも長ければ、シグナルインテグリティ解析が必要になると考えられます。電気長は、プリント基板の場合で物理長の約50~60%程度です。電気長を考慮する経路は送信デバイス~受信デバイスまでの全ての経路であり、送信側デバイスを搭載するプリント基板の伝送路の配線、送信側コネクタ、ケーブル、受信側コネクタ、受信側デバイスを搭載するプリント基板の伝送路、これら全てを含みます。

信号品質劣化の原因

信号品質が劣化する原因は、主として以下の4つが存在すると考えられます。

①インピーダンス不整合での反射による波形歪やリンギング

②電源リプルによるジッタの影響

③隣接信号からのクロストークによる影響

④配線損失

また、これらに加え、複数信号(クロック同期回路でのクロック信号とデータ信号線など)のスキューもシグナルインテグリティの一つとする場合が見受けられますが、このコラムにおいては、単純に信号の品質という意味でこれらを含めないこととし、プリント基板での配線における信号品質の劣化を引き起こす様々な原因とその対策について触れていければと思っています。(但し差動信号での各信号間スキューはこのコラムでの対象となります。)