技術コラム Column

- models

- 連載コラム :シミュレータで使用されるモデル

IBISモデル

目次

はじめに

「シミュレータで使用されるモデル」の第2回では、IBIS(Input/Output Buffer Information Specification)モデルについて見て行きたいと思います。IBISモデルは1993年に「IBIS Open Forum」が設立され、IBIS Version1.1がリリースされて以来、30年以上の歴史があります。設立当初、既に回路シミュレーションで使用するモデルとしてSPICEモデルがありました。然しながら、SPICEモデルは内部回路をそのまま記述する仕様であり、半導体メーカにとっては、回路情報やプロセス情報といった秘匿性の高い情報が競合他社へ漏洩することを懸念し、モデルを必要とするセットメーカとは秘密保持契約を結んだ後に提供を行う必要がありました。このため流通性が悪く、セットメーカにとっては入手までに多くの時間を要しました。また、SPICEモデルは、回路規模が大きくなると解析に多大な時間を要するという問題もありました。そこで考え出されたのが、I/O部分の特性とパッケージ部分の特性を一体化して記述したIBISモデルです。SPICEモデルは受信端での波形品質だけでなく、回路の機能検証にも使用できますが、IBISモデルは内部回路などの情報を含まず、専ら波形品質を高速に検証することを目的として開発されました。

IBISは何度もバージョンアップか繰り返され、応用範囲も多岐に渡ってきていますが、このコラムではIBISの全体像の理解を目的として、基本部分に絞って解説してみたいと思います。

バッファモデルとパッケージモデル

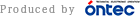

図1は、IBISの出力モデル(左側青枠内)及び入力モデル(右側青枠内)の基本構成で、それぞれ、バッファモデル(図の赤枠部分)とパッケージモデル(図の緑枠部分)に分かれています。図2の半導体の構造例では、バッファモデルは、ダイに焼き付けられた回路(I/O部分のみ)を、パッケージモデルは、ボンドワイヤ~リードフレームといったICの配線部分をモデル化しています。

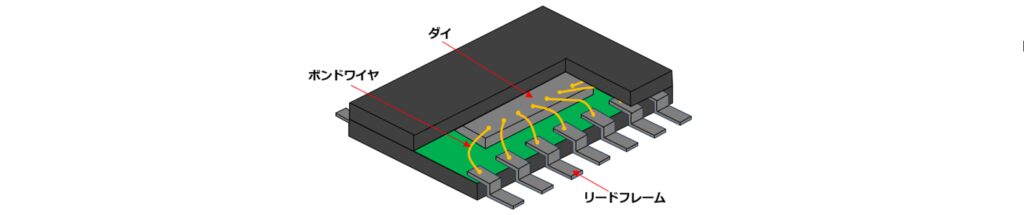

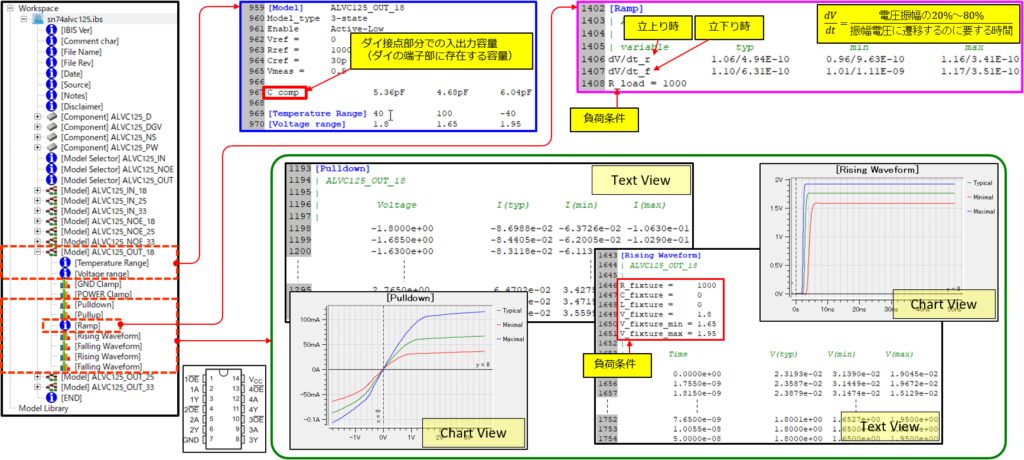

IBISモデルファイルは、テキスト形式のため、メモ帳やテキストエディタなどで中身を確認することが出来ます。(拡張子は“.ibs”となっています) また、SINTECS社の“IBIS Development Studio2”というIBISモデルファイルの中身を確認するのに大変便利なツールが公開されています。こちらは、IBISモデルを作成・編集するためのツールですが、ビューアとエディタの一部の機能だけであれば無償で利用することが出来ます。セクションごとにグループ化してツリー構造で表示され、キーワードやコメントを色分けして表示してくれます。また、Pullup、Pulldownなどの特性を表すテーブルについては、テキストだけでなく、グラフ表示することができるので視認性が高まります。このコラムではこのツールを使用してIBISモデルファイルの中身を探っていこうと思います。図3に、このツールの表示例を示しておきます。

図4は、IBISモデルファイルの全体像をIBIS Development Studio2で見たものです。青枠部で囲われている部分はヘッダ記述部と呼ばれ、IBISバージョンや作成日、メモ、著作権情報などが記載されます。緑枠部で囲われている部分はコンポーネント記述部と呼ばれ、パッケージモデルの情報に加え、ICの各ピンとバッファモデルとが関連付けされます。最後に赤枠部で囲われている部分がバッファモデル記述部分でIBISモデルのコア部分となっています。[Pullup]、[Pulldown]、[POWER Clamp]、[GND Cramp]、[Rising Waveform]、[Falling Waveform]などのキーワードがあり、これらは図5のような、I-V特性、V-t特性がテーブルの形式で記述されます。

図4右側ペインのテキスト表示部で行頭が「|」で始まる緑文字の行はコメント行となっています。また、青文字[ ]で括られている文字はキーワードと呼ばれています。キーワードの後にはサブパラメータや定義値が記述されます。キーワードごとにどのようなサブパラメータを持つかは予め決められています。

IBISモデルファイルの中身を紐解く

図6は、Texas Instruments社様のSN74ALVC125のIBISモデルの例となります。ここでは、最上位階層のキーワードである、[Component]、[Model Selector]、[Model]という3つのセクション(キーワード)について詳しく説明します。

[Component](図6の緑枠)は、パッケージモデルに関する情報、各ピンの名称と各ピンに割り当てられているモデル名またはモデルセレクタ名が記載されます。この例のように、[Component]は1つのIBISモデルファイルの中に複数存在する場合があります。(この例ではパッケージ違いにより4種類の[Component] が存在しているので、ユーザは、どのコンポーネントを使用するか(この例ではどのパッケージを使用するか)を選択する必要があります) [Package]キーワードに続いてパッケージの寄生成分をL/R/Cの集中定数で記載するサブパラメータ(R_pkg、L_pkg、C_pkg)(緑塗りの部分)があります。ここに入れられるパッケージ寄生成分は全ピン共通となっています。これは必須項目であり、IBIS製作者は必ず入れなければなりません。[Pin]キーワードに続いて各ピンに割り当てられているモデル名またはモデルセレクタ名のどちらかが記載されます。(例ではモデルセレクタ名が割り当てられています)(赤塗りの部分) また、ピンごとのパッケージ寄生成分がL/R/Cの集中定数で記載(R_pin、L_pin、C_pin)されている場合があります。(青塗りの部分) この定義値はオプションとなっており、[Package]キーワードのR_pkg、L_pkg、C_pkgは全ピン共通のパッケージ寄生成分でしたが、こちらはピンごとの違いも網羅しているため、利用できる場合はこちらを利用する方が解析精度を高めることが出来ます。(ここでは触れませんが、 [Define Package Model]というキーワードにより、ピン間結合も考慮されているオプションが用意されている場合があります。また、数百MHz~GHz帯での通信を行うICでは、IBISファイルとは別にSパラメータファイルを提供している場合があります。IBISファイルで提供されるパッケージ寄生成分の情報は集中定数であるため、GHz帯の解析には向きませんが、Sパラメータは分布定数モデルであり、高周波帯にもピン間結合にも対応出来ます。)

[Model Selector](図6のピンク枠)は、1つのピンに割り当てられるモデル候補が複数ある場合に導入されます。例えば、レジスタ設定でドライブ能力や終端抵抗値など複数の設定が可能な部品や、この例のように使用する電源電圧によってモデルが分けられている場合、などがあります。 [Model Selector]がある場合は、ユーザは用途によりどのモデルを使用するかを選択する必要があります。

[Model]は、バッファモデルに関する情報が記載されます。(図1の赤枠、Buffer Modelの部分で、パッケージ寄生成分(パッケージモデル)は含みません。) 図6の赤塗り部分を見るとバッファモデルが複数のピンで共有されているのがわかります。(このICには同一のバッファが4つあり、それぞれ同じ特性であるため、1,4,10,13番ピン(xNOE)、 2,5,9,12番ピン(xA)、 3,6,8,11番ピン(xY)に、それぞれ、ALVC125_NOE_*、ALVC125_IN_*、ALVC125_OUT_*、と同じモデル名が割り当てられています。

バッファモデルでは、出力ドライバの静特性として[Pullup]、[Pulldown]キーワードが、クランプダイオードの静特性として[POWER Clamp]、[GND Clamp]キーワードが定義されており、それぞれにI-V特性がテーブルの形で表されます。(図7の緑枠部分) また、出力ドライバの動特性として[Ramp]キーワードや、[Rising Waveform]・[Falling Waveform]キーワードが定義されています。 [Ramp]は必須キーワードで、立上り/立下り時の時間あたりの電圧変化量が単一の数値で表される(図7のピンク枠部分)のに対し、 [Rising Waveform]・[Falling Waveform]はオプションのキーワードであり、[V-t特性]としてテーブル形式で表されます。(図7の緑枠部分) 当然、[Rising Waveform]・[Falling Waveform]が存在する場合は、こちらを使用した方が、精度が良くなります。バッファモテルでは、更に、ダイ接点部分での入出力容量(ダイの端子部に存在する容量)としてC_Compというサブパラメータが定義されています。(図7の青枠部分)

最後に

現在、SI解析を必要とするようなディジタルICにおいては、これらを供給している殆どの半導体メーカはIBISモテルを公開しています。2008年8月にリリースされたIBISバージョン5.0では、高速なSerDes(シリアライザ/デシリアライザ)回路のシミュレーションに向けたモデルフォーマットであるIBIS-AMIが追加され、高速SerDes回路に伝送線路を含めたシミュレーションを高い精度を確保しつつ、短時間で実行することが可能となりました。また同バージョンからPower Aware IBISという電源電圧ノイズを考慮する事が可能なモデルが制定されました。これにより、PDNモデル(電源配線モデル)を用意することで、DDRメモリなど、同時に複数のデータ信号がスイッチングする際に発生する電源ノイズによる波形への影響を解析できるようになりました。 2015年9月にリリースされたIBISバージョン6.1ではIBIS-AMIがPAM4にも対応するようになりました。このように、IBISモデルは市場ニーズに合わせてバージョンアップが頻繁に行われており、SI解析にはなくてはならないモデルとなっています。

御参考URL

Sintecs社 IBIS Development Studio 2.0