技術コラム Column

- emc

- 連載コラム :EMI低減の道しるべ

プレーン共振対策 – 線電源と面電源での違い

目次

プレーン共振対策 – 線電源と面電源での違い

電源配線が長くなると、放射エミッションで問題となる1GHzを超えない低い周波数でもプレーン共振を引き起こす可能性があります。 ICが電源端子から引き込む過渡電流の帯域がこの共振周波数に達すると、PDNを励起し、放射エミッションを増大させます。 一般的にプレーン共振周波数は、基材の比誘電率に加え、電源プレーンとGNDプレーンが重なる部分の形状によって決まると言われています。 多層プリント基板では電源層、GND層を設けることが多く、電源配線を線電源にするべきか、面電源にするべきかを議論される場合があります。

本連載の第2回では、プレーン共振対策としてコンデンサやπ型フィルタを追加することで得られる放射エミッション低減効果について、線電源と面電源の場合での違いを見ていきたいと思います。

実験基板の構成

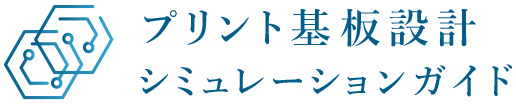

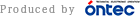

今回行った実験の構成は前回と同じであるため、詳細は第1回のコラムを御参照下さい。 使用した実験基板を図1~3に示します。図1は前回のバリエーション⑥と同じもので、これをベースに共振対策コンデンサを実装出来るように図2のような基板を準備しました。 この基板はL1(部品面)に共振対策用にコンデンサを最大4個(パスコンと合わせて5個)まで実装出来るようにしています。 更には、線電源、面電源の差を検証するため、図3のような基板も準備しました。こちらは、図2の基板からL3の線電源を面電源に変更したものです。 使用した対策コンデンサはパスコンと同じで、全て村田製作所株式会社様の「GCJ188R71H104KA12D」で、サイズは1608、容量は0.1uFです。

放射エミッション測定結果

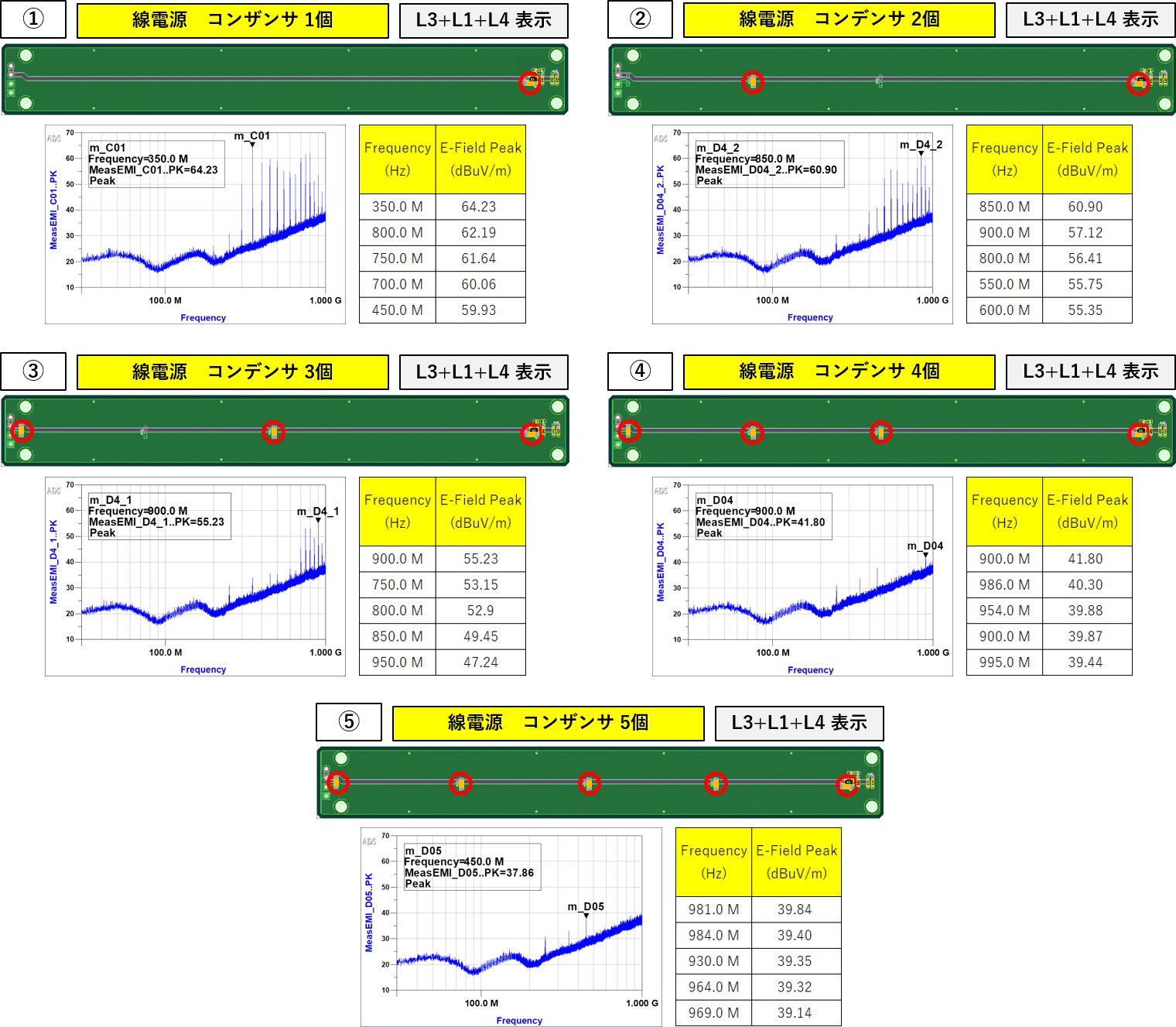

図4~図5は、今回の実験基板における放射エミッションの試験結果です。 図4の①~⑤は、それぞれ、線電源ベースの基板で、プレーン共振対策用のコンデンサが無い場合(コンデンサはパスコンの1個のみ)と、1~4個追加した場合(コンデンサはパスコンを含めて2~5個)のものです。 図5の⑥~⑦は、それぞれ、面電源ベースの基板にプレーン共振対策用コンデンサが無い場合(コンデンサはパスコンの1個のみ)と4個追加した場合(コンデンサはパスコンを含めて5個)のものです。 パターン図、実装図は、L1,L3,L4を重ねて表示しています。 赤〇部分はコンデンサが実装されている箇所を表しています。 試験結果は、3m 法での放射エミッション試験結果とその右隣りに電界強度(ピーク値)の高い順に上位5番目までのピーク値と、その周波数を掲載しています。

測定結果の考察

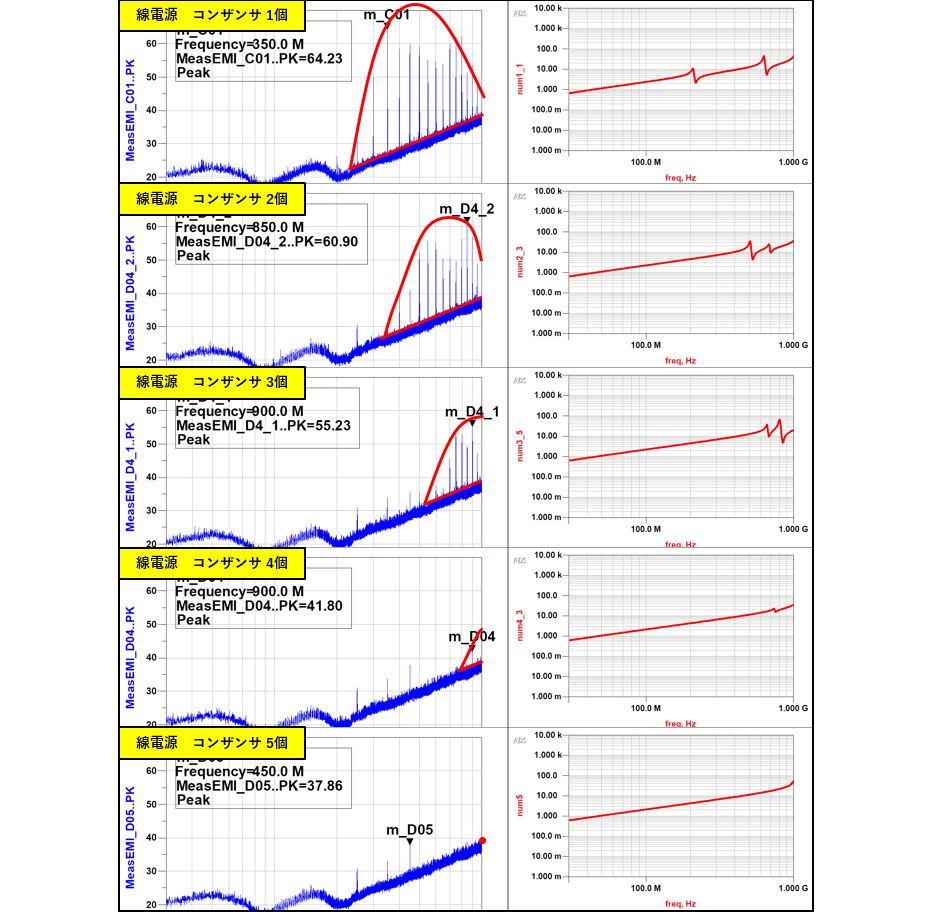

図6の左側は、線電源ベースの基板において、プレーン共振対策用のコンデンサを0~4個追加した時の放射エミッション試験の結果を並べています。 共振対策用コンデンサを追加することにより、電界強度のピークは高周波側にシフトし、小さくなっています。 (コンデンサを挿入する位置によっては電界強度のピークとなる周波数が変わります。) 放射エミッション試験結果の右側には、電磁界解析ツールを使用してこの基板のPDNインピーダンスの解析を行った結果を掲載しています。 ピークの周波数に少しずれがありますが、共振が存在する部分に、電界強度のピークも存在していることが読み取れます。 このことから、PI解析により事前に共振対策を施すことで、結果として放射エミッションを低減することが出来ると考えられます。

次に、面電源ベースの基板について調べた結果を図7に示します。 ここでは、プレーン共振対策用のコンデンサを0個と4個の2種類のみ掲載しています。 面電源の場合、共振対策用コンデンサを4個追加しただけでは、放射電界強度は小さくなりませんでした。 PDNインピーダンスの解析結果においても共振は解消されていません。 面電源では、線電源のように簡単には共振をなくすことができないことがわかります。

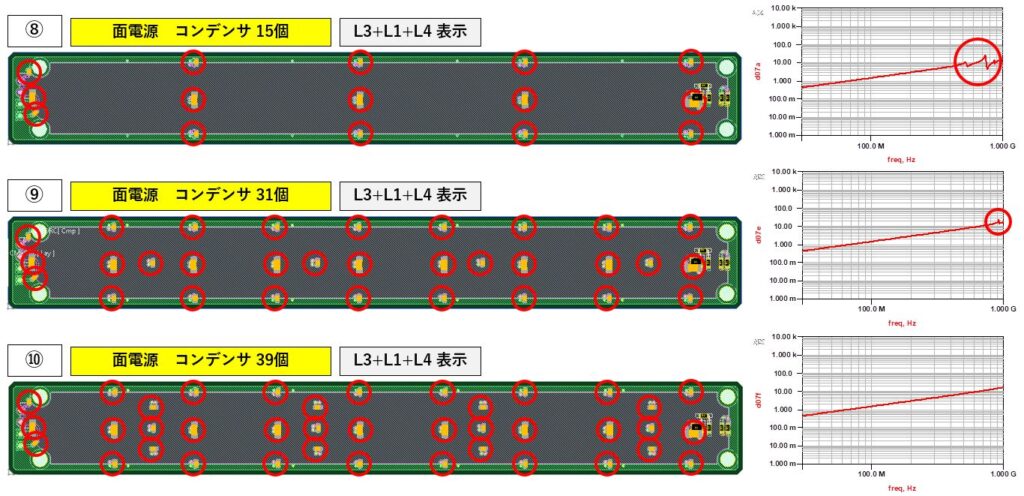

追加解析として、図8の左側のように、面電源ベースの基板に対し、プレーン共振対策用のコンデンサ15~39個まで増やした場合を想定して、PDNインピーダンスの解析を行いました。 図8の右側が、その解析結果です。 面電源の場合、コンデンサの数を増やしても共振周波数を高周波側へ大きくシフトさせることが難しく、共振のQ値もあまり小さくならないため、対策が難しいことがわかります。 追加解析では、39個のコンデンサを追加し1GHzまでの共振がようやく収まりました。 残念ながら、これらは放射エミッションの実測データはありませんが、これまで見てきた放射エミッションの実測値とPDNインピーダンスの共振との相関性から、面電源では、コンデンサによるプレーン共振対策が難しいことは想像に難くないと思います。

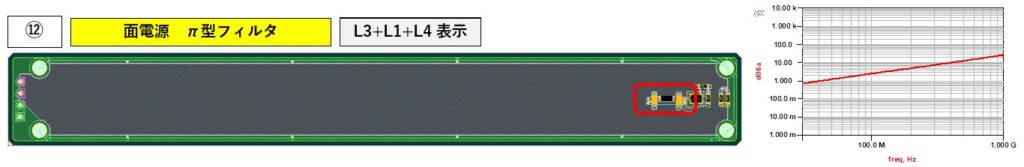

続いて、コンデンサによる対策ではなく、フィルタによる対策を施したもので解析してみます。

図9、図10左側はそれぞれ、線電源ベース、面電源ベースの基板に対し、電源ラインにπ型フィルタを追加したもので、図9、図10の右側がPDNインピーダンスの解析結果です。 π型フィルタのビーズ部分には、前回のコラム同様に株式会社村田製作所様の「BLM18RK121SN1」を使用しました。(このビーズの特性は前回の記事を参照して下さい)

線電源、面電源共に、π型フィルタによりPDNへの励起が抑制され、共振対策用のコンデンサが無くても共振が無くなっています。 (一般的に、他のデバイスからの高周波ノイズの流入を防ぐ効果も期待出来るため、電源ノイズに敏感なデバイス(アナログ系ICやPLLなど)の誤動作を防ぐ効果も期待できます。) 残念ながら図10の構成(面電源、π型フィルタ)の実測データは無いので、次の機会にでも実測してみようと思います。 (図9の構成(線電源、π型フィルタ)に関する実測データは前回のコラムの⑧の構成を参照して下さい。)

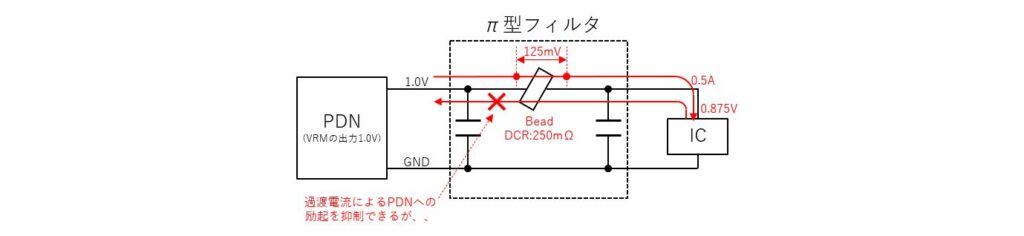

ビーズのDC抵抗値(今回使用したビーズで250mΩ(max))は非常に大きいので、電源電圧が低く、大電流が流れるICに適用する場合には電圧降下に注意する必要があります。 図11のように、消費電流が0.5AであるICの電源端子にDC抵抗250mΩのビーズを使用すると、ビーズのDC抵抗による電圧降下が125mVにもなります。 VRMの出力電圧とこのICの電源電圧が共に1.0Vの場合、ICの電源端子部の電圧は0.875Vまで下がり、電源電圧の許容範囲を満たせなくなる可能性があります。 このような場合には、予めVRMの出力電圧を上げておくなどの調整が必要になります。

最後に

今回のコラムでは、プレーン共振対策としてコンデンサやπ型フィルタを追加することで得られる放射エミッション低減効果について、線電源と面電源の場合での違いを見てきました。

線電源と面電源のどちらにおいても、コンデンサの追加による放射エミッションの低減効果が確認出来ましたが、面電源では、対策コンデンサの追加による効果が乏しく、必要なコンデンサの数が増加する傾向にあります。 その結果、共振対策が難しくなるだけでなく、無駄なコストも発生するため、パターンに流れる電流値や許容される温度上昇などにより必要なパターン幅に制約はありますが、電源のパターン幅を不必要に太くすることは避けるべきです。 π型フィルタの挿入は両者に効果的ですが、導入にあたっては、事前に使用するビーズのDC抵抗に注意し、ICの電源電圧の許容範囲を超えないか確認しておくのが無難です。

また、今回の実験結果から、PDNインピーダンスの解析で確認された共振と放射エミッションに相関があることを確認しました。 プレーン共振対策は、電源ラインの電位差が最も大きく変動する位置(共振の腹と呼ばれる)を特定し、デカップリングコンデンサやスナバ回路を追加することで行われますが、PDNインピーダンスの解析により見つかった共振点を除去する対策を施すことでも、放射エミッションを低減させることが可能であることがわかりました。