技術コラム Column

- pi

- 連載コラム :パワーインテグリティ(PI)改善のポイント

パワーインテグリティ(PI)とは?

パワーインテグリティ(またはPI)とは?

パワーインテグリティ(またはPI)とは、プリント基板の電源ラインにおける電源品質のことを表します。近年、基板の小型化、FPGA・ASIC・SoCなどの大電流化・低電圧化・高速化が進み、電源回路の設計やパターン設計が次第に困難になってきています。製品の小型化が進むと、プリント基板上の部品実装が高密度化し、電源層・GND層に信号線を配線する必要が生じたり、それらの層を貫くビアが増えたりすることで、理想的な電源やGND配線が難しくなります。また、FPGA・ASIC・SoCなどの低電圧・大電流化により、配線抵抗による電源電圧低下が無視できなくなっています。更には、これらのデバイスが大電流を高速にスイッチングすることに伴い、パスコンの高周波特性や配置などにも気を配らなければなりません。これらを背景に、近年、パワーインテグリティへの関心がますます高まっています。

インプットインピーダンスとターゲットインピーダンス

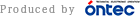

パワーインテグリティにおいて、始めに知っておいてほしいものとして、インプットインピーダンスとターゲットインピーダンスがあります。図1は、PDN(電源配線ネットワーク)の例として、プリント基板配線の断面図を示しています。この例では、PDN上に、電源モジュール(VRM)、出力コンデンサ、プリント基板配線、パスコン、オンパッケージキャパシタ、BGAのダイが存在します。ここでBGAの電源端子からVRM側配線を見た時のインピーダンスをインプットインピーダンスと呼び、パワーインテグリティの指標となる基本パラメータとなっています。

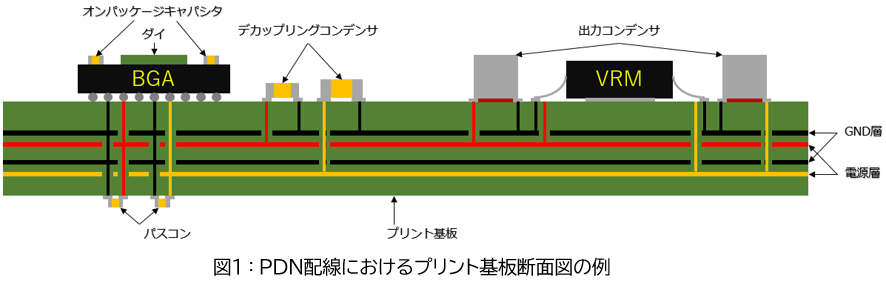

図2の赤線は、インプットインピーダンスを表しています。黒色の点線は、インプットインピーダンスが超えてはならない閾値を表し、これをターゲットインピーダンスと呼んでいます。PDN設計では、インプットインピーダンスがターゲットインピーダンスを超えないようにする必要があります。図2の例では、10KHzと10MHz付近でインプットインピーダンスがターゲットインピーダンスを超えており、負荷となるICがこの周波数帯を含む電流を引き込むと、ICの許容電源電圧範囲を超える可能性があるため、対策が必要と考えられます。

インプットインピーダンスを悪化させる要因

インプットインピーダンスを悪化させる要因は、周波数帯ごとに異なります。図2では、要因が異なると考えられる周波数帯ごとに3つに色分けをしています。

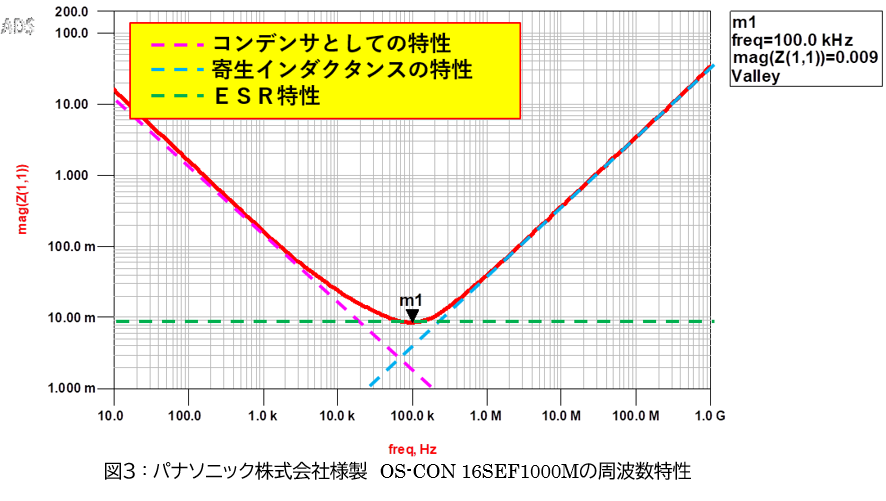

VRMがDCDCコンバータの場合、その発振周波数付近+アルファまでは(図2の黄色部分)、VRMの制御が効果的に働くため、インピーダンスを低く抑えられますが、それ以上の周波数帯になると、DCDCコンバータの制御が効かなくなり、インピーダンスが高くなっていきます。+アルファと書いたのは、これを抑えるために出力コンデンサがVRMの直近に配置されるためです。出力コンデンサは、容量の大きな電界コンデンサなどを用いる場合が多く、低周波数帯(数100KHz程度まで)ではコンデンサとしての役割を果たしますが、周波数が高くなると寄生インダクタンス成分が支配的となり、インピーダンスが高くなるため(図3)、インプットインピーダンスの低減には役に立たなくなります。

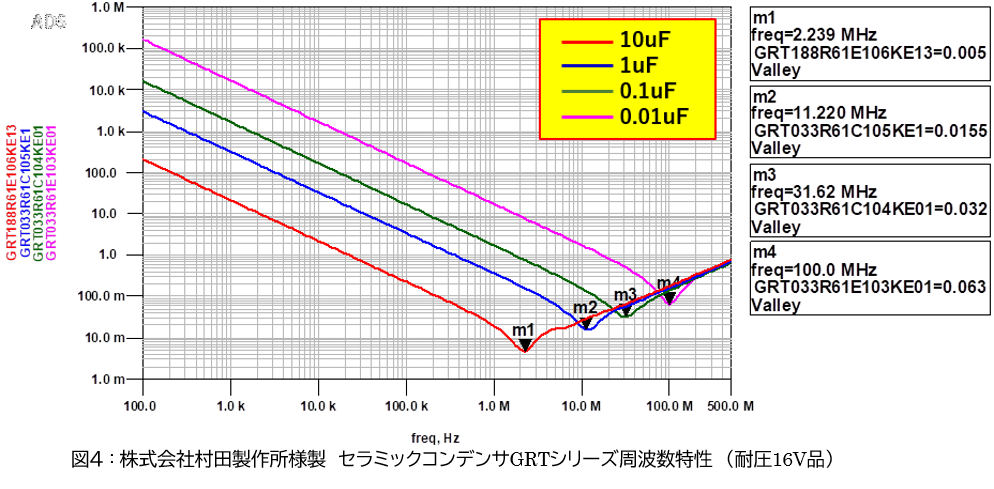

数100kHz~数10MHz付近までは(図2の緑色部分)、プリント基板の配線、IC直近に配置されるパスコンなどの影響が支配的な周波数帯となります。この周波数帯においては、パスコンの数・容量・配置や、電源・GNDラインの配線により、大きく性能が左右される部分となります。参考までに、図4にパスコンとしてよく使用されるセラミックコンデンサ((株)村田製作所様製)の周波数特性を示しておきます。

更に数10MHzを超えると(図2の青色部分)、プリント基板上でのパスコンでは対策しにくい周波数帯となるため、この周波数帯での電源品質が必要なデバイスについては、デバイスメーカが、ダイやパッケージ上にコンデンサを実装するオンダイキャパシタやオンパッケージキャパシタを設けている場合があります。

最後に、DCに近い周波数帯では、基板配線やPDN上に直列に配置されるコイルやビーズなどのDC抵抗による電圧降下が主な要因となります。