技術コラム Column

- si

- 連載コラム :シグナルインテグリティ(SI)改善のポイント

高速シリアル通信とイコライゼーション (2)

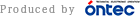

前回(第9回)のコラムでは高速シリアル通信においてイコライザが必要となる背景と、一般的に送信側に実装される FFE について説明しました。 今回(第10回)のコラムでは、受信側に実装される CTLE および DFE について、その基本的な動作を簡単に整理し、シミュレーションによる効果の検証を行っていこうと思います。

Continuous-Time Linear Equalizer (CTLE)

Continuous-Time Linear Equalizer (CTLE)は、連続時間線形イコライザとも呼ばれており、伝送チャンネルにより減衰した高周波成分を補償し、逆に相対的に大きくなってしまった低周波成分を抑圧する機能を持つアナログ方式のイコライザです。 一般的に、受信デバイス側に実装され、Decision Feedback Equalizer (DFE) の前段に置かれます。

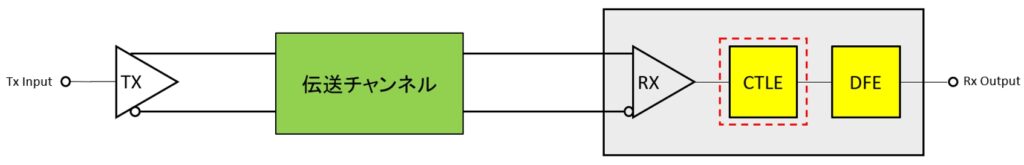

図16左は、SerDesや高速デジタルI/Oレシーバの一般的な2ポール1ゼロアクティブCTLEの実装例です。 RS,CSが低域のポールを形成、RD,CPがゼロを形成しています。 (RD,CPは高域のポール形成にも寄与します。)

一般的にCTLEは、図16右の青色スペクトラムのような周波数特性となっており、伝送チャンネルにより減衰した高周波成分を補償し、図16右の緑色スペクトラムのような、ナイキスト周波数までフラットな周波数特性にするのが目標になります。

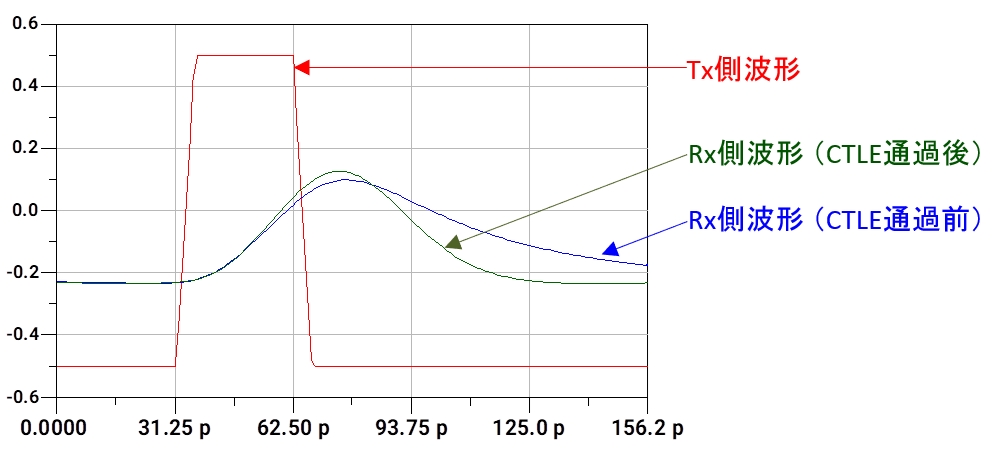

図17は、送信デバイスからの単一パルスに対する受信デバイスの応答波形を解析した例を示しています。 赤色は送信側波形、青色は受信側のCTLE通過前波形、緑色は受信側のCTLE通過後波形となっています。

CTLE通過前の波形を見ると、立下り後に尾を引くような波形が観測されますが、CTLEにより、立上り/立下りのなまりの改善が見られます。 もともと、CTLEは誘電損失などによる伝送チャンネルの周波数減衰を補正するために導入されたものですが、この波形からシンボル間干渉の軽減にも繋がると考えられます。

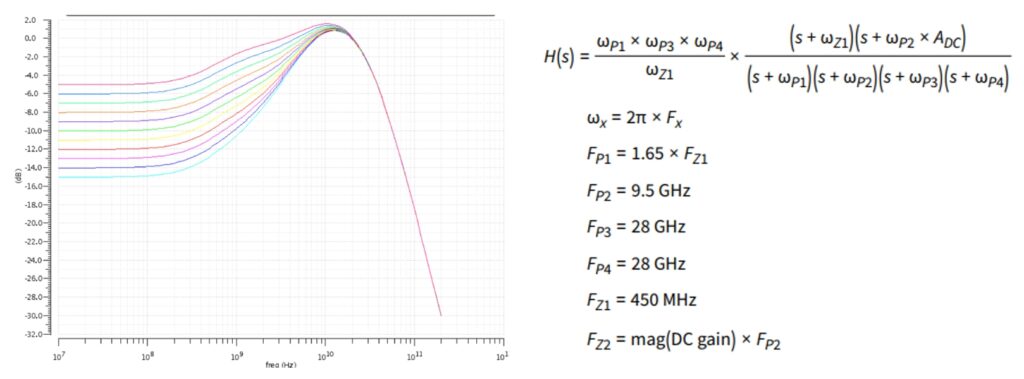

図18は、PCI Express Gen5の規格から抜粋した、32GT/s 動作モードにおけるCTLEのプリセットごとの周波数特性および伝達関数を示しています。 このモードでは、CTLE に対して11種類のプリセットが定義されており、各プリセットは、図に示すようにDC ゲインの違い(-5dB~-15dB)となっています。 図18左側の周波数特性を見ると、低周波(450MHz以下)ではほぼDC gainの値、中周波領域(ナイキスト周波数前後)でゲインが持ち上がり、高周波領域(28GHz以上)では大きく減衰する周波数特性になっています。

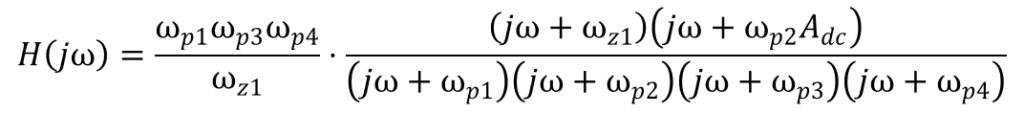

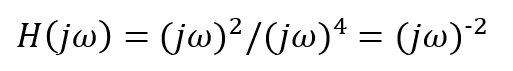

これを踏まえて、図18右側の伝達関数について少し考察してみます。 伝達関数はS領域で表されているので、これを周波数領域で表すと次のようになります。

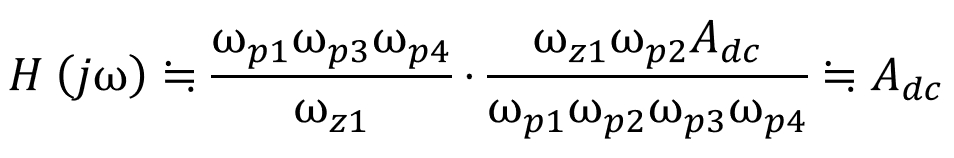

この式に対し、低周波領域(ωがゼロやポールに対して十分に低い周波数領域)、中周波領域(ナイキスト周波数:16GHz前後)、高周波領域(ωがゼロやポールに対して十分に高い周波数領域)の3つの領域に対するゲインを考えます。

・低周波領域

低周波領域 ω ≫ ωp1 , ωp2 , ・・・ と、仮定すると、

・中周波領域

分子のゼロ ωZ1 , ωp2 Adc が寄与して、ゲインの落ち込みを部分的に補正します(持ち上げます)。

・高周波領域

高周波領域 ω ≪ ωp1 , ωp2 , ・・・ と、仮定すると、

となるので、振幅はω-2に落ち、-40 dB/dec の傾きになります。

これらの考察から、式がグラフと一致していることが直感的に理解できるかと思います。

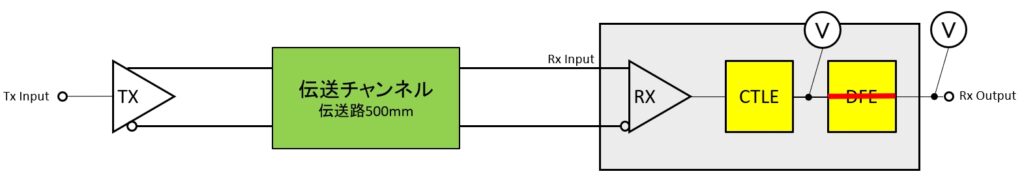

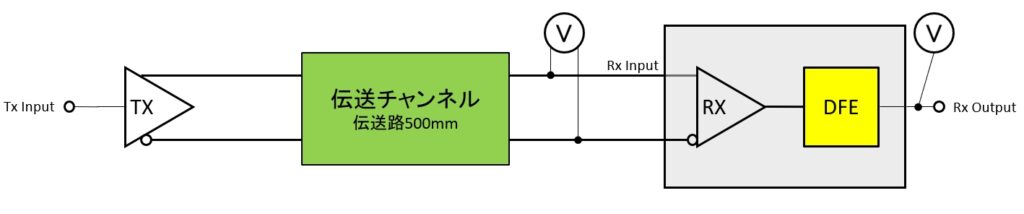

それでは、CTLEにより補償された信号がどのような波形となるのかをシミュレーションにより検証してみたいと思います。 ADSでは、CTLEをビヘイビアモデルとして先ほどの式を適用して出力波形が導き出されます。 検証するシステムを図19に示します。 送信側で32GbpsのNRZ信号(疑似ランダムビット列)を入力します。 伝送路はFFE検証時と同様、FR4基板上の配線(100Ω差動、500mm、損失-13.24dB)だけとしています。 (図のCTLE後段のDFEはバイパスしています。)

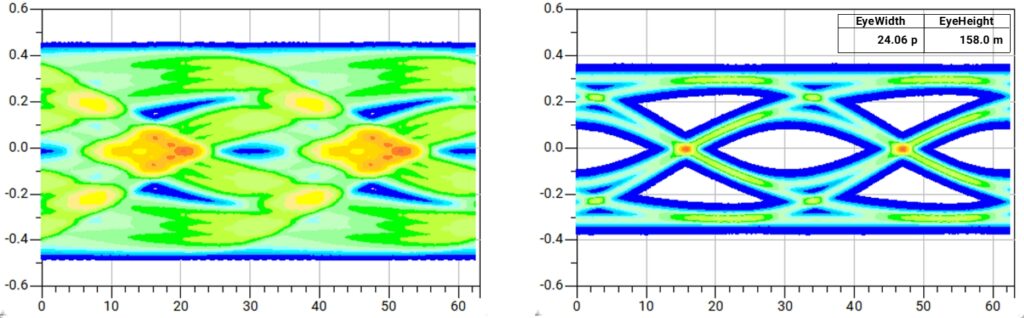

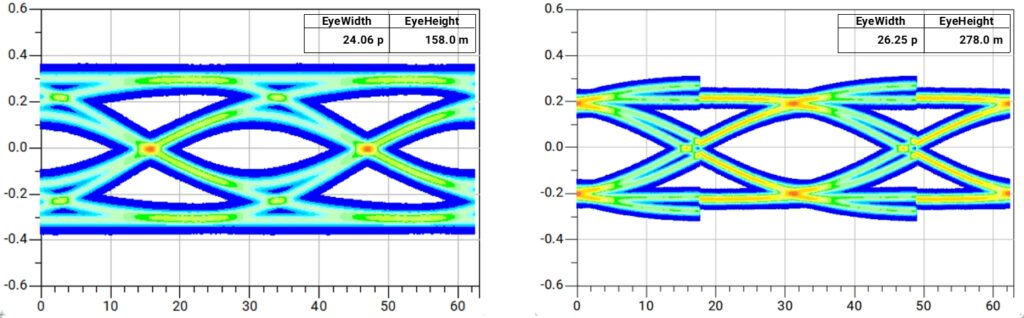

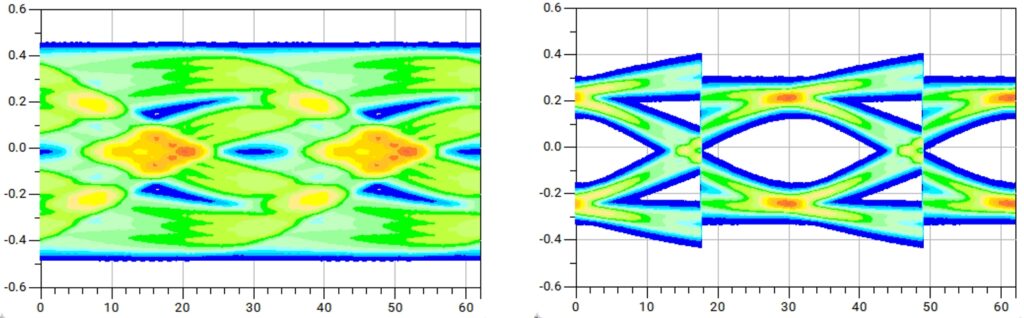

図20は、シミュレーションで得られた結果で、伝送チャンネルを通過後の、CTLE適用前後のアイ波形を比較しています。 左側がCTLE通過前、右側がCTLE通過後の波形であり、本ケースではPCIe Gen5の6dBプリセットを適用しています。 CTLE通過前はアイがほぼ完全に閉じていますが、通過後は高周波成分が補償され、明確にアイが開いていることが確認できます。

一般に、図21のように、CTLEの後段にはDFEが配置されます。 図22では、CTLE通過後にDFEを挿入した場合と、挿入しない場合のアイ波形を比較表示しています。 左側がDFE無し、右側がDFE有りの波形です。 DFEは3タップ構成としています。ADSでは、伝送チャンネルの特性に応じてDFEのタップ係数を自動最適化できるため、係数はその機能を利用して決定しています。 今回のケースでの最適化結果は、{Tap係数1: -0.048780, Tap係数2: 0.002999, Tap係数3: 0.005270 } となりました。

DFEを適用することで、CTLEでは補償しきれなかったシンボル間干渉がさらに低減され、アイ開口が一段と改善されていることが分かります。 CTLEとDFEを直列に組み合わせることで、伝送チャンネルで劣化した波形を効果的に再構築できることが示されています。 また、DFEを適用すると、波形に非線形な部分が現れていることがわかります。 これについては、この後のDFEの章にて解説したいと思います。

Decision Feedback Equalizer (DFE)

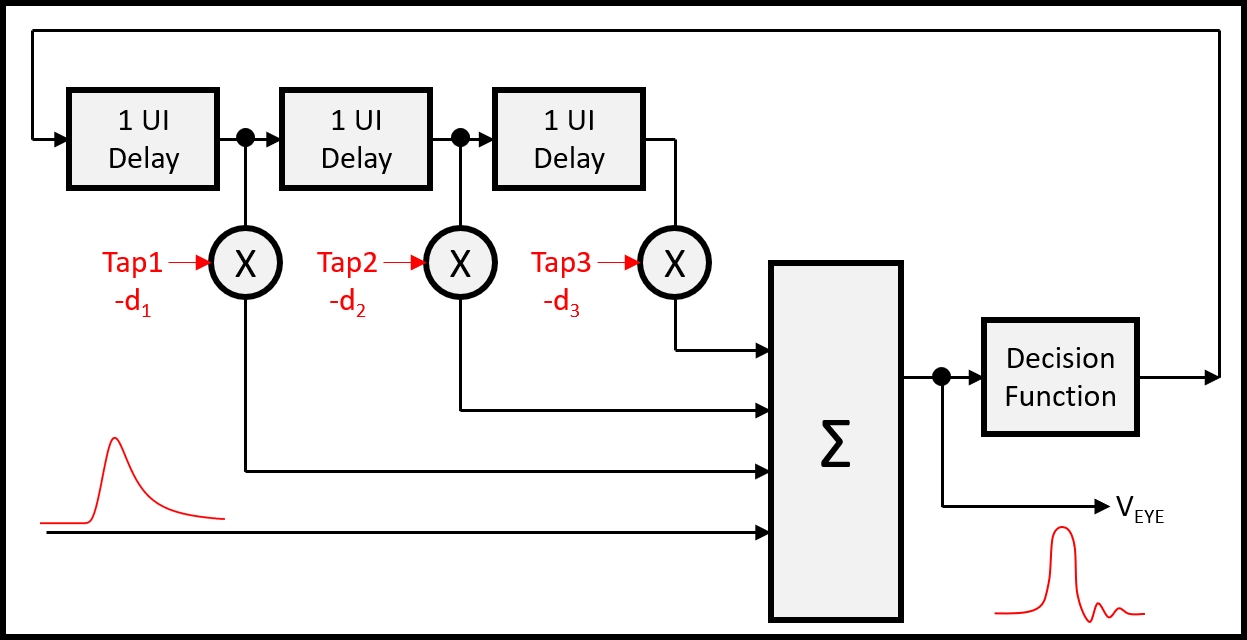

Decision Feedback Equalizer(DFE)は、判定帰還型イコライザとも呼ばれています。 Feed Forward Equalizer (FFE)と同様に、シンボル間干渉によって生じる波形の歪みを補正し、より正確な判定を行えるよう設けられる非線形イコライザの一種で、DFEは専ら受信側に設けられます。 システムが許容する伝送チャンネル特性などに応じて、シンボル間干渉が後続ビットへ及ぼす影響範囲が決まりますので、その影響を補償するために必要なタップ数が定められます。

図23は、3タップのDFE構成図を示したものです。 図の右側にあるDecision Functionは、いわゆるスライサであり、入力波形をサンプリングして0か1(または−1か+1)を判定します。 この判定結果はフィードバックされ、過去3ビット分の結果がシフトレジスタに保持されます。 各ビットはあらかじめ設定されたタップ係数と乗算された後、劣化した入力波形に補正信号として加えられ、再びスライサに入力されます。 シンボル間干渉には、現在のビットより後に現れるPostカーソル成分と、前に現れるPreカーソル成分がありますが、DFE は補正に判定済みのビットを使用する構造のため、補償できるのはPostカーソル成分に限られます。

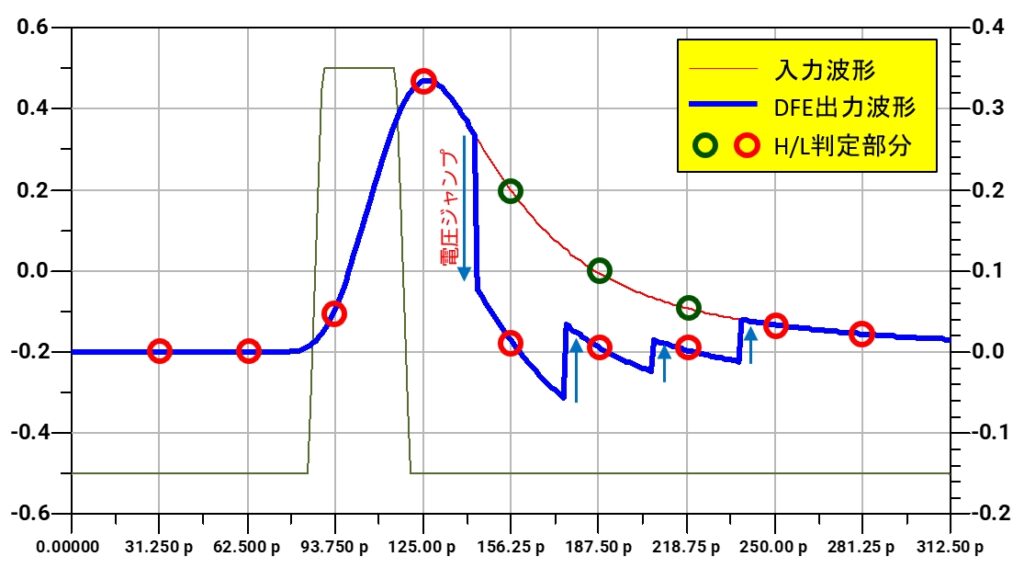

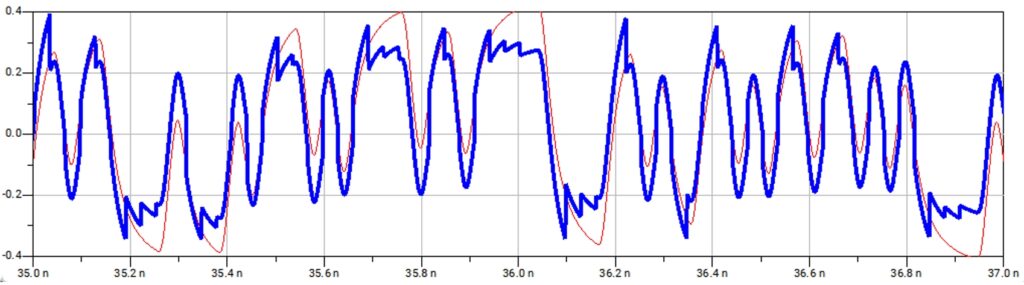

図 24 は、伝送チャンネルを通過して劣化した入力波形(赤色細線)と、DFE によって補正された出力波形(青色太線)を重ねて示したものです。 赤〇は H/L 判定部分(31.25psec 周期)を表しています。 入力波形にはポストカーソル ISI が生じており、本来の判定タイミングにおいても過去シンボル由来の電圧成分が残留しています。

DFEでは、過去のシンボル判定結果を用いてフィードバック補正を行い、この残留しているシンボル間干渉の成分を打ち消すような係数に調整されています。 その結果、DFE出力波形では、各判定タイミングにおいて過去シンボルに起因する干渉成分が相殺され、判定点での干渉成分が0に近づくよう補正されていることが確認できます。

スライサによる判定結果がシフトレジスタへ転送されると、各タップ係数に応じたフィードバック補正が加えられます。 判定結果が離散値であるため、フィードバック量が段階的に変化することによる電圧ジャンプが生じます。 図のDFE出力波形からもこの電圧ジャンプの発生が確認できます。 3タップ構成の場合、シフトレジスタの出力値が、

[R1,R2,R3]

[1,0,0] または [+1,-1,-1]

[0,1,0] または [-1,+1,-1]

[0,0,1] または [-1,-1,+1]

[0,0,0] または [-1,-1,-1]

と4回の変化が生じるため、図のように電圧ジャンプも4回発生します。 この電圧ジャンプがアイ波形表示時の非線形箇所発生の原因になります(図22右側参照)。 一般的にR1→R2→R3と決定ビットが遷移するに連れ、タップ係数が小さくなるため、電圧ジャンプも次第に小さくなっていき、最後の電圧ジャンプ後は補正がかからなくなり、入力波形と同じ波形になります。

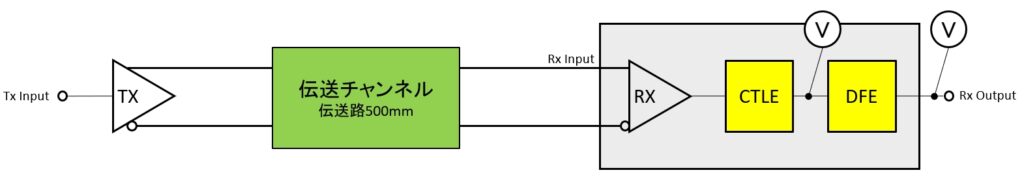

それでは、DFEにより補正された信号がどのような波形となるのかをシミュレーションにより検証してみたいと思います。 検証するシステムを図25に示します。 これまで同様、送信側で32GbpsのNRZ信号(疑似ランダムビット列)を入力します。 伝送チャンネルも同様に、FR4基板上の配線(100Ω差動、500mm、損失-13.24dB)だけとしています。 DFEは3タップ構成とし、タップ係数はシミュレータが自動最適化した値を使用しています。

図26、図27にADSによるシミュレーション結果を示します。 図26はDFE通過前後のアイ波形で、左図がDFE通過前、右図がDFE通過後です。 同様に、図27はDFE通過前後のトランジェント波形で、細い赤色の波形がDFE通過前、太い青色の波形がDFE通過後です。 アイ波形を見るとDFEを適用することで、アイパターンが開口しているのが確認できます。 トランジェント波形を見るとノコギリ波状の形状が現れますが、これは前節で説明した通り、DFEの仕組みによって生じる電圧ジャンプが原因です。 このため、アイパターンには非線形な部分が見られますが、これは特に問題となるものではありません。

次にDFEのタップ数の違いがアイ開口に与える影響について検証してみようと思います。

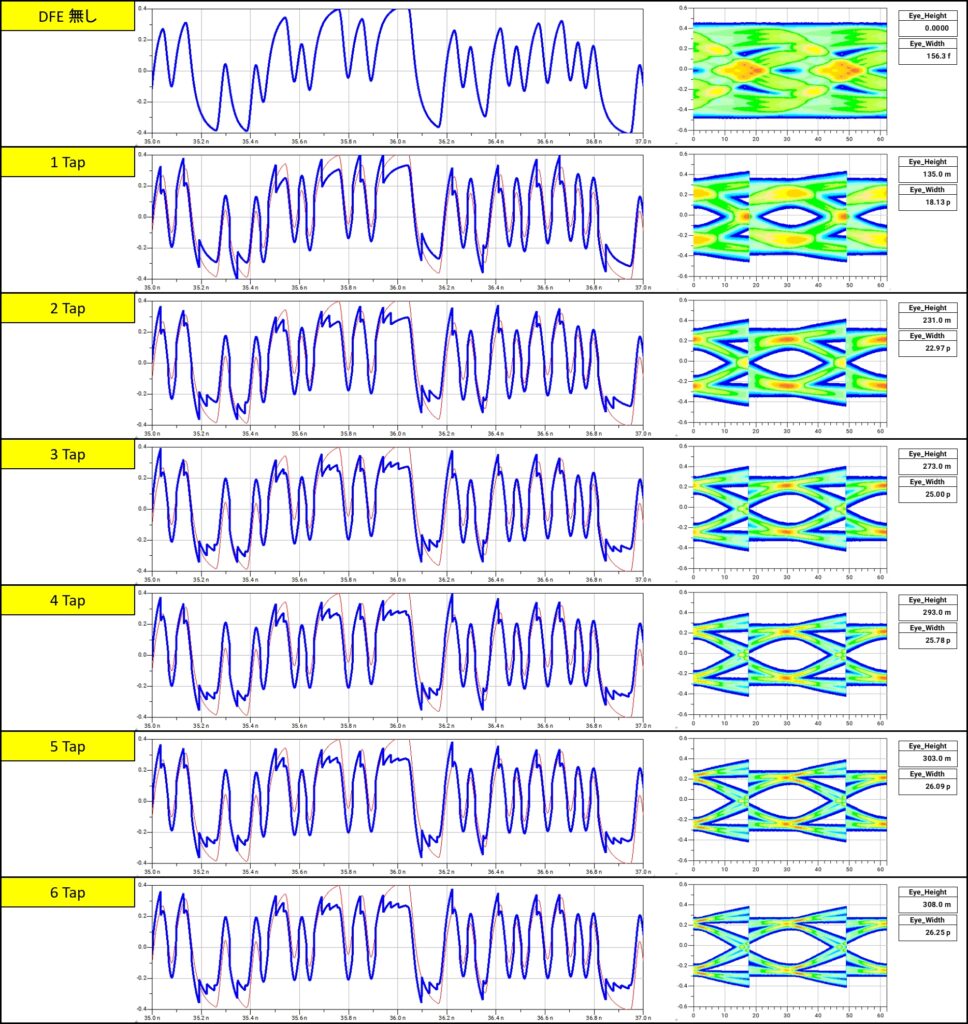

図28は、DFEのタップ数を1から6まで変化させた場合のトランジェント波形とアイ波形を、ADSによるシミュレーションで得た結果です。 前項と同様に、送信側はイコライザを使用せず、32 GbpsのNRZ信号(疑似ランダムビット列)を出力させ、伝送チャンネルには、FR-4基材を用いた長さ500 mmのマイクロストリップ差動配線を設定しています。 受信側ではCTLEを無効とし、DFEのみを有効化した状態で、DFEタップ数がアイ開口に与える影響を比較・評価しました。 (タップ係数は、それぞれ、シミュレーションが出力する最適値をそのまま使用しています。)

タップ数を増やすにつれてアイ開口は大きくなっているのが確認できます。

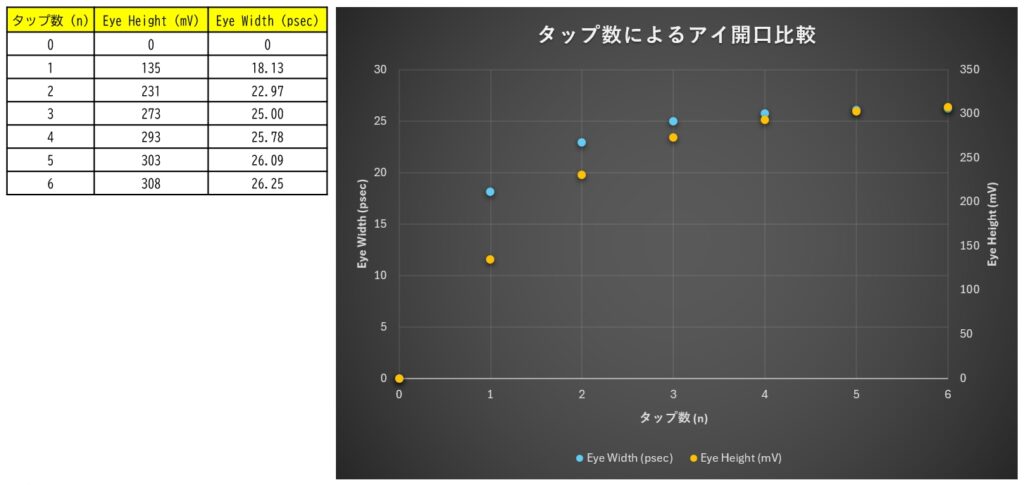

図29は、タップ数によるアイ高さとアイ幅を一覧表にしたものと、これをグラフ上にプロットしたものです。

タップ数を増やしていくと補償効果は徐々に頭打ちとなり、この例では4~5タップ以上ではほとんど改善が見られなくなりました。 伝送チャンネルに合わせた最適なタップ数を選ぶことが、回路規模や消費電力の増大を抑えつつ、波形品質を担保することに繋がるということが理解できるかと思います。

最後に

昨今の10GHzを超えるような高速シリアル通信では、損失の大きい伝送チャンネルを使用すると、受信端(受信機器のコネクタ部や受信デバイスのピン)で観測されるアイ波形は完全に閉じてしまい、オシロスコープでサンプリングした生波形で評価を行うことが出来ません。 そのため、生波形からではなく、受信デバイス内のイコライザを模擬し、補正された波形の品質により評価されています。

もはやチャンネル損失を極力小さく抑える従来の設計だけでは、必要な信号品質を確保できなくなりました。 また、イコライザだけで十分な波形品質が確保できない場合には、チャンネル途中にリタイマやリドライバといった中継デバイスを挿入することで、劣化した信号を再整形することもよく行われるようになりました。 これは、「損失を抑えるチャンネル設計」から、「チャンネル損失を前提とした設計」にパラダイムシフトしていることを意味します。

本コラムでは、FFE、CTLE、DFE といった各イコライザの原理とその効果を個別に検証してきましたが、実際のシステムではこれらが組み合わされて相互作用するため、システム全体として最適化する必要があります。 (個々の最適値の組み合わせが全体としての最適値にはなりません。) 各種規格に基づくリンクトレーニングなどによって自動的に最適化される場合もあれば、固定チャンネルを前提とした設計においては、ユーザがイコライザに対し適切な設定値を決める場合もあるかと思います。 電磁界シミュレーション技術を活用すれば、これらを高い精度で迅速に評価できるため、非常に有効な手段になり得ると考えています。