技術コラム Column

- si

- 連載コラム :シグナルインテグリティ(SI)改善のポイント

高速シリアル通信とイコライゼーション(1)

高速シリアル通信における信号劣化の主要因には、伝送チャンネル損失、信号反射、ジッタ、シンボル間干渉(ISI)、クロストーク、外来ノイズなど、多くの要素が存在します。 これらのうち、信号反射、クロストーク、外来ノイズなどについては、配線や部品・コネクタ部でのインピーダンス不整合を可能な限り抑える、外来ノイズやクロストークの影響を受けにくくするためにシールドを施すなどでの対策が中心になります。

一方、プリント基板上の配線やケーブルなど、伝送路の導体損失、誘電体による高周波成分の減衰や、群遅延特性による信号劣化については、イコライザを使用することで非常に効果の高い対策を行うことができます。 近年の高速シリアルインターフェースでは信号周波数が飛躍的に伸び、イコライザなしでは信号品質の確保が難しくなっており、PHYには例外なくイコライザが実装されています。

伝送路損失による高周波成分の減衰はCTLE (Continuous-Time Linear Equalizer)やFFE(Feed Forward Equalizer)により補償可能であり、伝送路損失が原因で発生するシンボル間干渉もFFEやDFE (Decision Feedback Equalizer)によってその影響を低減することができます。

本コラムでは、これらのイコライザ技術に焦点を当てて解説していきます。 本稿は全3回構成で、前編(第9回)では、高速シリアル通信においてイコライザが必要となる背景と、一般的に送信側に実装される FFE の基本的な動作を簡単に整理し、シミュレーションによる効果の検証を行っていこうと思います。 続く中編(第10回)では、受信側に実装されるCTLEおよびDFEについて解説します。 最後の後編(第11回)では、イコライザによる補償が困難で不可避的に発生する特性インピーダンスの不連続点に着目し、配線設計の最適化によって波形品質を改善した事例を紹介する予定です。

高速デジタル信号におけるイコライザの必要性

イコライザの必要性を理解するために、まずは伝送路の長さ(損失)や信号速度が、信号波形にどの程度の影響を与えるのかをシミュレーションを使用して確認していきます。 (本稿で示すシミュレーション結果は、すべて Keysight Technologies 社の Advanced Design System(以下、ADS と表記)を用いて取得したものです。)

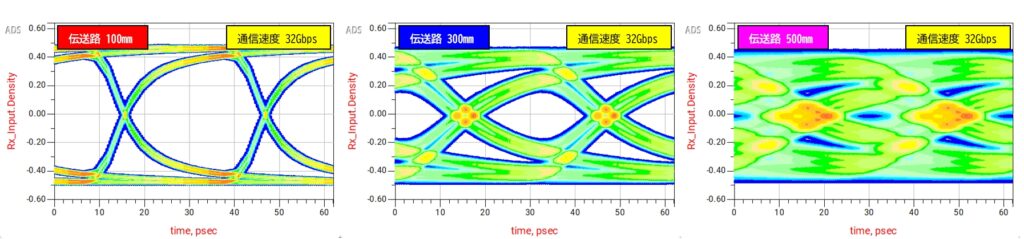

ここでは、32Gbps NRZ信号を例に、伝送路の長さを100mm、300mm、500mmと変化させた場合に、受信端の波形がどのように変化するのかを検証します。 (伝送路はFR4基板上の100Ω差動配線のみとしています。)

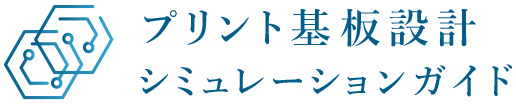

図1に、シミュレーションの構成図とその結果を示します。 左下図は伝送チャンネルの透過特性(Sdd21)、中央下図は32Gbps(Pulse Width: 31.25ps, Rise/Fall Time: 5ps)の単発パルスに対する応答波形、右下図は 0→1→0→1→0 と変化するパルス列に対する応答波形をそれぞれ示しています。

透過特性を見ると、伝送路が長くなるほど損失が増加していることが確認できます。 例えば、このシステムのナイキスト周波数である16GHzでは、100mmの配線で-2.649dBだった損失が、500mmでは-13.24 dBまで増加しています。

次に、単発パルスに対する応答波形を見ると、伝送路が長くなるほど立上り(立下り)が遅くなり、波形がなまっていく様子が確認できます。 さらに、0→1→0→1→0 と変化するパルス列の応答波形では、前段シンボルに対するチャンネル応答のテール(尾部)が、後続シンボル期間にまで影響を及ぼし、信号の振幅が小さくなるなどの歪みが生じているのが確認できます。 これはシンボル間干渉(ISI)と呼ばれ、BER(ビットエラー率)を悪化させる主要な原因の一つとなっています。

続いて、信号速度の違いが受信端波形にどのような影響を与えるかについて確認します。

信号速度が速く(ナイキスト周波数が高く)なったとしても、伝送チャンネルの応答特性そのものが変化するわけではないので、応答波形のなまり方や減衰の傾向自体は同じです。 一般的に高速化に伴って立上り/立下り時間が速くなりますが、これによって応答波形のなまり具合を大きく変化させることはなく、むしろ、エッジ部分の高周波成分が増えるため、アイを開く方向に働くはずです。

では、なぜ信号速度が高速化するとアイが閉じるのでしょうか。

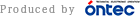

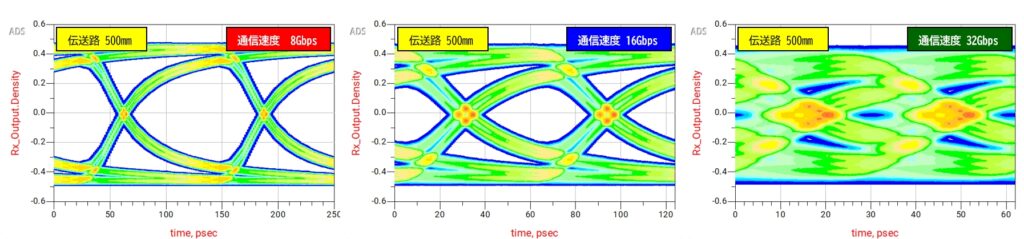

図2は、信号速度を8Gbps(Pulse Width: 125ps, Rise/Fall Time: 20ps)、16Gbps(Pulse Width: 62.5ps, Rise/Fall Time: 10ps)、32Gbps(Pulse Width: 31.25ps, Rise/Fall Time: 5ps)と変化させた時の応答波形を解析したものです。 前項と同様に、左下図は単発パルスに対する応答波形、右下図は 0→1→0→1→0 と変化するパルス列に対する応答波形をそれぞれ示しています。 伝送路は先ほどと同様、FR4基板上の100Ω差動配線で、伝送路長は500mmに固定しています。

信号速度が速く(周期が短く)なると、1シンボルに割り当てられる時間が相対的に短くなります。 これは、ちょうど伝送路が長くなった場合と同様に、応答波形が十分に Low レベルまたは High レベルへ到達する前に、次の立上り/立下りエッジのタイミングがやってくることを意味し、信号速度が速くなるほど、このエッジは相対的に早いタイミングで現れることになります。 その結果、伝送路が長くなった場合と同様、図2の波形のように前段シンボルに対するチャンネル応答のテール(尾部)の影響を受けたまま次のシンボル期間に入るため、信号の振幅が小さくなるなどの歪みが生じ、アイが閉じることになります。

図3は、伝送路長を100mm、300mm、500mmとした場合に、受信端で観測された信号波形のアイ解析結果です。 伝送路 300mmまではアイの開口が確認できますが、500mmになると、アイが完全に閉じてしまっています。 この状態になると、無対策では確実に通信が出来なくなることは容易に想像出来るかと思います。

図4は、伝送路は500mm固定とし、通信速度を8Gbps、16Gbps、32Gbpsとした場合に、受信端で観測される信号波形のアイ解析結果です。 (信号立ち上がり時間はそれぞれ20ps、10ps、5psです。) 通信速度 16Gbpsまではアイの開口が確認できますが、32Gbpsになると、アイが完全に閉じてしまっています。

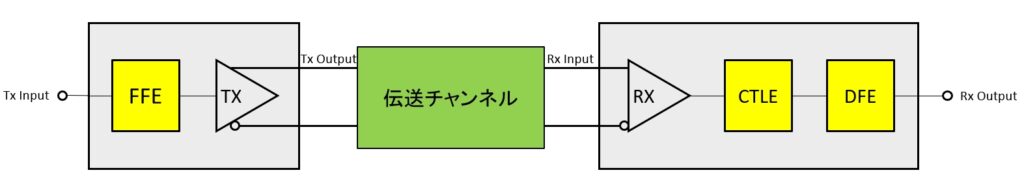

このように、「アイ閉じ」は伝送路の損失増加や信号の高速化とともに顕著になるため、現在の高速デジタル設計では、これを補償するために、送信側(TX)・受信側(RX)の双方でイコライゼーション技術を適用することが一般的となっています。 図5に高速シリアル通信システムの構成例を示します。 送信側では、かつて主流であった単純なプリエンファシス/ディエンファシス(2タップ FFE 相当)に代わり、多タップ構成のTX-FFE(FIR フィルタ)が一般的に使用されています。 Preカーソル/Mainカーソル/Postカーソル係数をリンクトレーニングで自動最適化する方式が主流で、PCI Express、Ethernet、USBなど多くの規格で採用されています。 さらに受信側では、CTLEにより高周波の減衰を補償した後、DFEで残存PostカーソルISIを除去する組み合わせが一般的です。 これらはUSB3.1/USB3.2 Gen2、PCI Express Gen5など、最新の高速シリアルインターフェース規格で広く利用されています。

次章以降では、FFE、CTLE、DFEそれぞれのイコライザについて、そのしくみとシミュレーションによる波形改善の検証を行っていこうと思います。

Feed Forward Equalizer (FFE)

FFE(Feed Forward Equalizer)は、高速シリアル通信において、伝送チャンネル特性に起因する信号エッジ部の高周波成分の減衰をあらかじめ補償することで、受信端における波形なまりやシンボル間干渉を低減する代表的なイコライザの一つです。

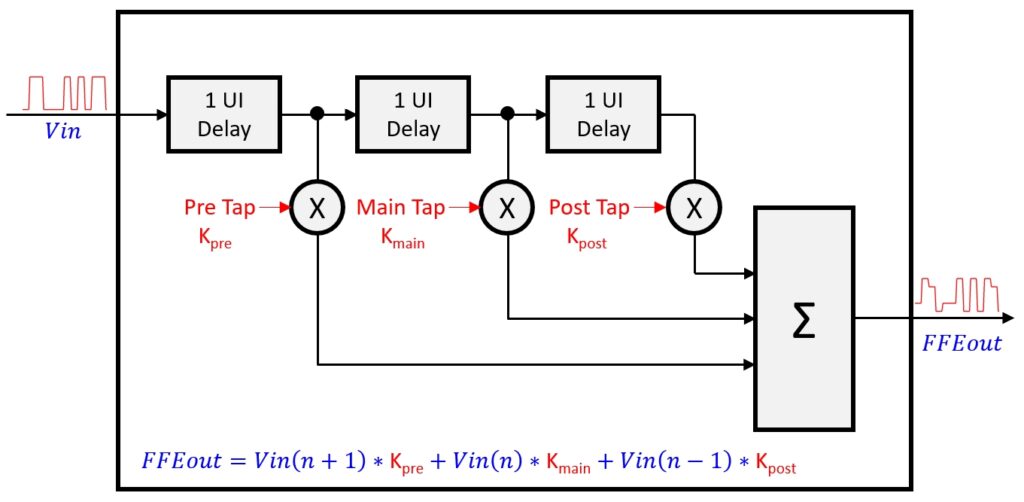

FFEは本質的にFIRフィルタと同じ構造を持ち、現在のシンボルに加えて前後複数シンボルを重み付けし、線形に加算することで、伝送チャンネルの逆特性に近い補償効果を与えます。 これにより、高周波成分の減衰や群遅延によって閉じてしまうアイパターンを効果的に改善できます。 FFEは各タップ(Preタップ、Mainタップ、Postタップ)の係数を調整することで、伝送チャンネルに合わせた補償を柔軟に実現できます。

図6は、3タップFFEの構成図を表しています。

伝送チャンネルによる送信ビット前後に生じるPreカーソルおよびPostカーソルの影響度合い、すなわちシンボル間干渉の大きさに応じて、各タップの係数が調整されます。 Mainカーソルは送信するビットそのものに対応するため、通常は最も大きな係数が割り当てられます。 また、一般的にはPreカーソルよりもPostカーソルの影響の方が大きいため、

Mainタップ係数 > Postタップ係数 > Preタップ係数

の順で係数が大きくなるのが一般的です。 ただし、伝送チャンネルの特性によっては、反射などの影響によりPreタップ係数の方が大きくなる場合もあります。 最終的な出力電圧は、図中に示す式によって決定されます。

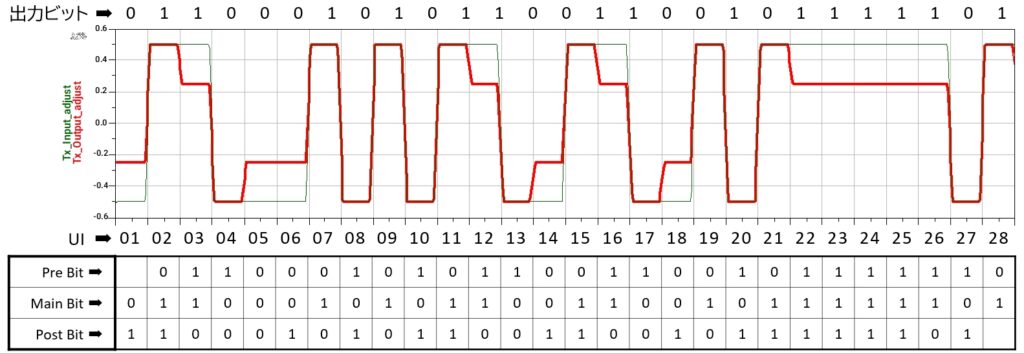

図7は、FFE の設定を 「Preタップ係数=0」、「Mainタップ係数=0.75」、「Postタップ係数=-0.25」 とした場合のFFE出力波形を示しています。 (薄い緑色がFFEへの入力波形、濃い赤色がFFEの出力波形です。) この設定はPCIe Gen5規格でのプリセット0に相当します。 FFEの入力は ±0.5 Vの2値信号であり、2タップ(3タップFFEですが、Preタップ係数が0であるため2タップ相当になります。)で構成されるため、出力には最大で22=4通りの電圧レベルが現れます。 この例では、±0.5V、±0.25Vの計4レベルが生成されています。

この設定ではPreビットへの補正はなく、MainビットがPostビットと同レベルの場合に、Postタップが作用して、25%の振幅低減補正がかけ続けられます。 入力がHigh連続(例:UI 22〜26)またはLow連続(例:UI 5〜6)の場合、振幅が抑制されていることが確認できます。

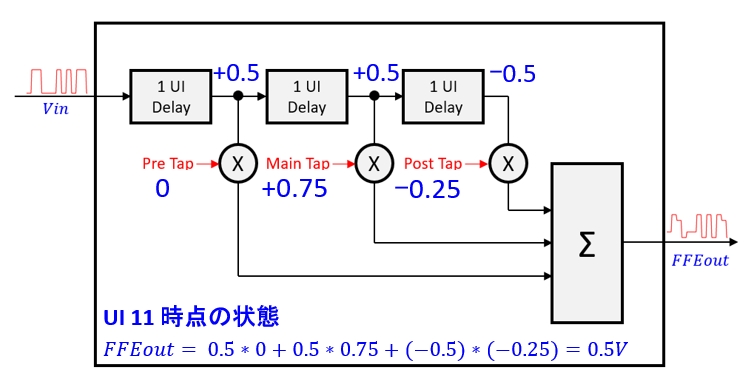

参考までに、UI 11時点でのFFE内部の状態を図8に示します。 FFEの出力は0.5Vとなっています。 他のUI時間についても同様に確認してみて下さい。

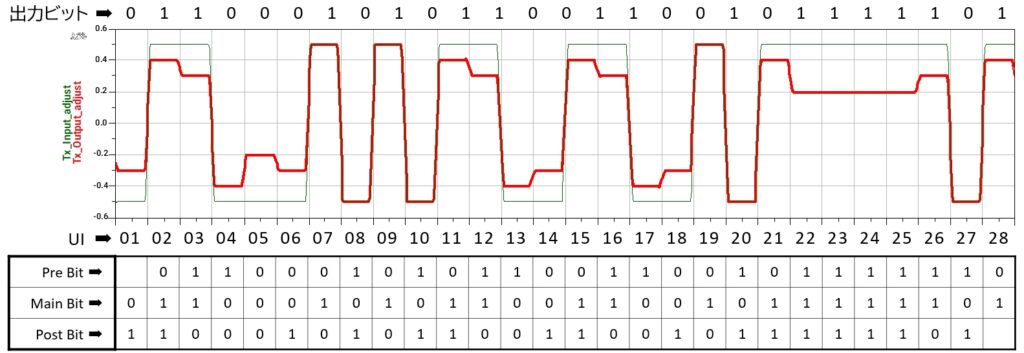

図9は、FFEの設定を「Preタップ係数=-0.10」、「Mainタップ係数=0.70」、「Postタップ係数=-0.20」とした場合のFFE出力波形を示しています。 (薄い緑色がFFEへの入力波形、濃い赤色がFFEの出力波形です。) この設定はPCIe Gen5のプリセット7に相当します。FFEの入力は±0.5 Vの2値信号であり、3タップ(すべてのタップ係数が非ゼロ)で構成されるため、出力には最大で2³=8通り の電圧レベルが現れます。 この例では、±0.5 V、±0.4 V、±0.3 V、±0.2 Vの計8レベルが生成されています。

入力がHigh連続(例:UI 22〜26)またはLow連続(例:UI 5〜6)の場合、振幅を抑制していることが確認できます。 また本例ではPreタップ係数も設定されているため、現在の振幅が低い(±0.2 V)状態で入力が反転すると、立上り/立下りを急峻にするように電圧が一時的に上昇(または下降)します。 これによりエッジに勢いが付与され(高周波成分が強調され)、信号の立上り・立下りが改善されます。 (例:UI 06、UI 26)

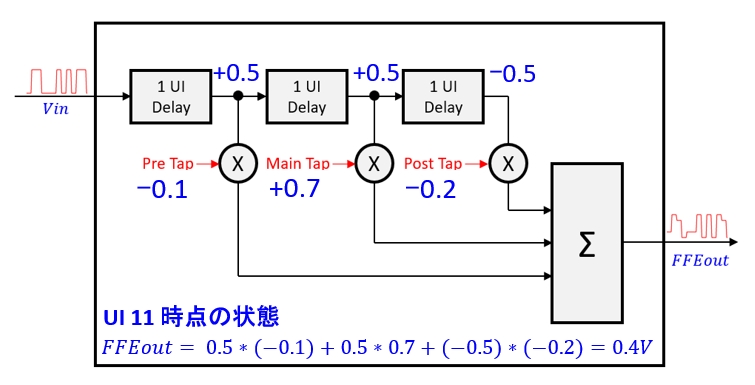

参考までに、UI11時点でのFFE内部の状態を図10に示します。 FFEの出力は0.4Vとなっています。 他のUI時間についても同様に確認してみて下さい。

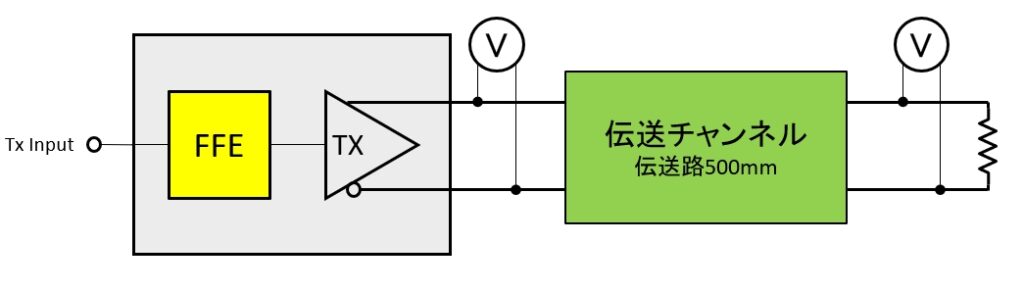

それでは、FFEにより補償された信号が受信側でどのような波形となるのかをシミュレーションにより検証してみたいと思います。 検証するシステムを図11に示します。 送信側に設けられたFFEに、32GbpsのNRZ信号(疑似ランダムビット列)を入力します。伝送チャンネルはFR4基板上の配線(100Ω差動、500mm、損失-13.24dB)だけとしています。

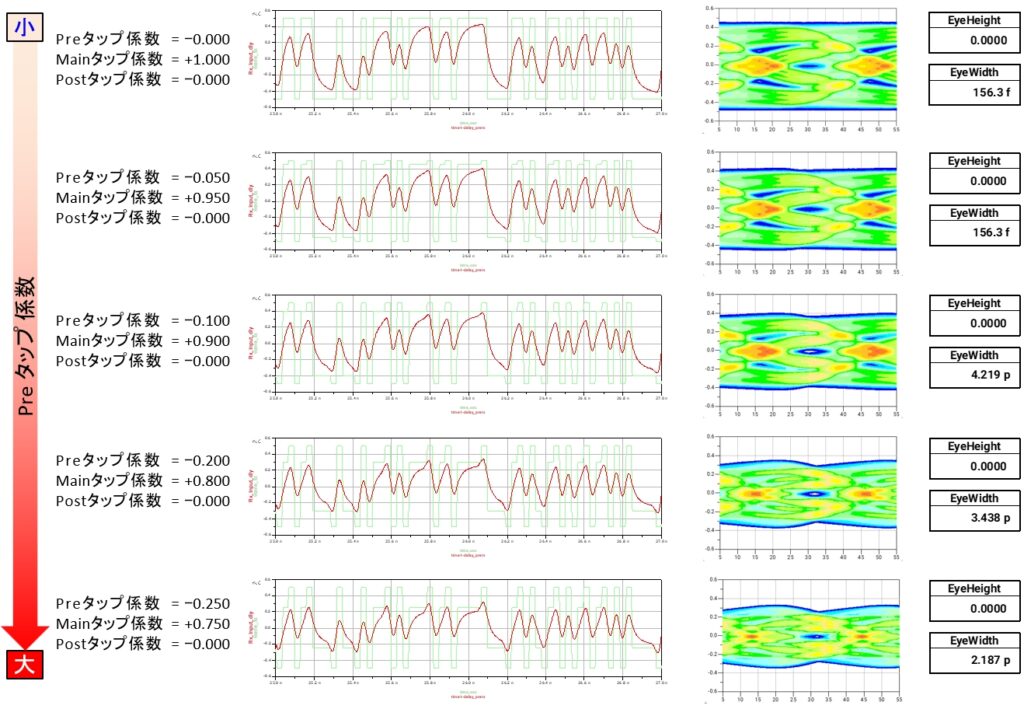

図12は3タップFFE (Pre/Main/Post) のPreタップ係数を変化させたときの終端抵抗両端の波形とアイパターンの変化を解析した結果です。 (各タップ係数の絶対値の合計は1となるようにしています。) 左列は各タップ係数の数値を示し、上から下に向かってPreタップ係数の絶対値を大きくなるようにしています(-0.000 (FFE無効) ~ -0.250の範囲で掃引)。 中央列は解析により得られたトランジェント波形で細い緑線がFFE適用後の送信波形、太い赤線が伝送チャンネル通過後の受信端での波形となっています。 右列は対応するアイパターンで、その横にアイ高さと幅を数値で表しています。

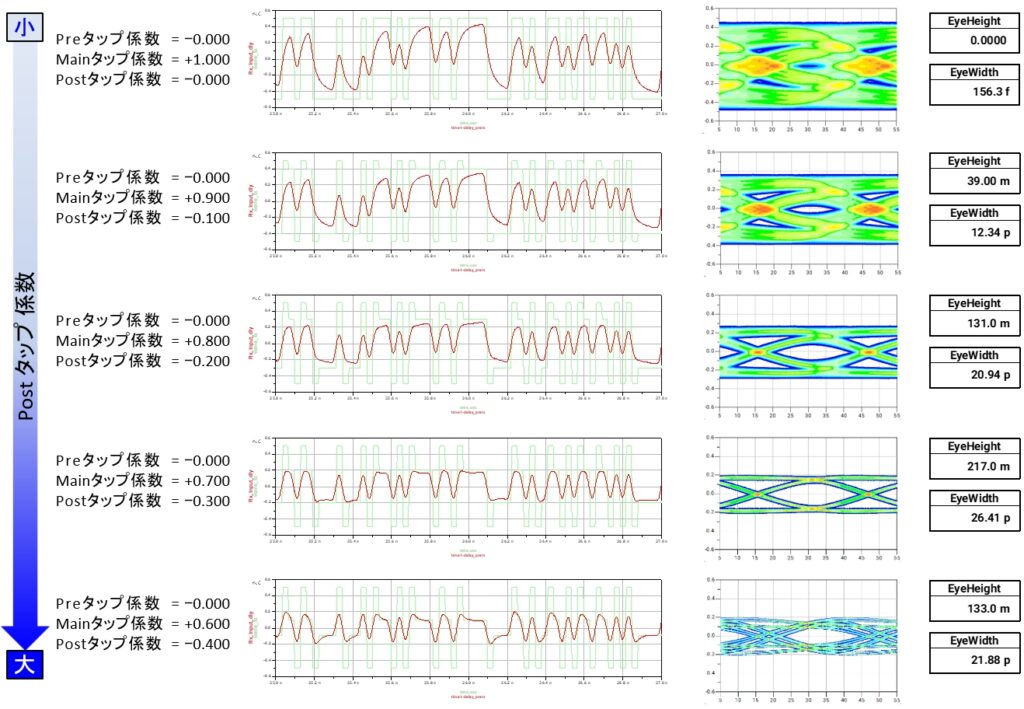

図13は、同様に3タップFFE (Pre/Main/Post) のPostタップ係数を変化させたときの受信端波形とアイパターンの変化を解析した結果です。 各タップ係数の絶対値の合計は1となるように調整しています。 左列は各タップの大きさを示しており、上から下に向かってPostタップ係数の絶対値を大きくなるようにしています(-0.000 → -0.400の範囲で掃引、一番上はFFE無効と同等)。 中央列は解析により得られたトランジェント波形で、細い緑線がFFE適用後の送信波形、太い赤線が伝送チャンネル通過後の受信端での波形となっています。 右列は対応するアイパターンで、その横にアイ高さと幅を数値で表しています。

波形全体を確認すると、FFEによる補正の無い一番上の波形(Postタップ係数が0の波形)では、高周波成分減衰により立上り/立下りエッジがなまっていることが確認できます。 Postタップ係数を大きくしていくにつれ、立上り/立下りエッジのなまりが改善されていき、Postタップ係数-0.4ではややオーバーシュート気味になっています。 アイ波形を見ると、FFEによる補正の無い一番上の波形では、アイが完全に閉じていますが、Postタップ係数を大きくしていくにつれ、アイが開口していくのが確認できます。 ただし、Postタップ係数-0.4まで補正を大きくすると、逆にアイが閉じる方向に逆転してしまうため、この係数以上は、過補償であるということがわかります。

また、FFEによる補正の無い一番上の波形では、信号全体が上下に大きく揺れ、H/L判定の閾値を跨いでいるか怪しい箇所が散見されます。 これはHighビットが連続すると信号の基線が高電圧側に、Lowビットが連続すると低電圧側にシフトするためです。 Postタップ係数を大きくしていくにつれ、信号全体の上下揺れは改善しています。

【参考】

一定時間内にHighのビットが多くなると高電圧側に、Lowビットが多くなると低電圧側にシフトし、直流成分に偏りが生じます。 高速シリアル通信では、一般的に8b/10bや128b/130bエンコーダ/デコーダなどの符号化/復号化技術が採用されており、信号のHigh/Low比率を均等化することで直流成分の偏りを抑えるとともに、ランレングス制限や制御コードの挿入により送信側と受信側の同期を確保し、さらにプロトコル制御やエラー検出の機能も実現できるように設計されています。

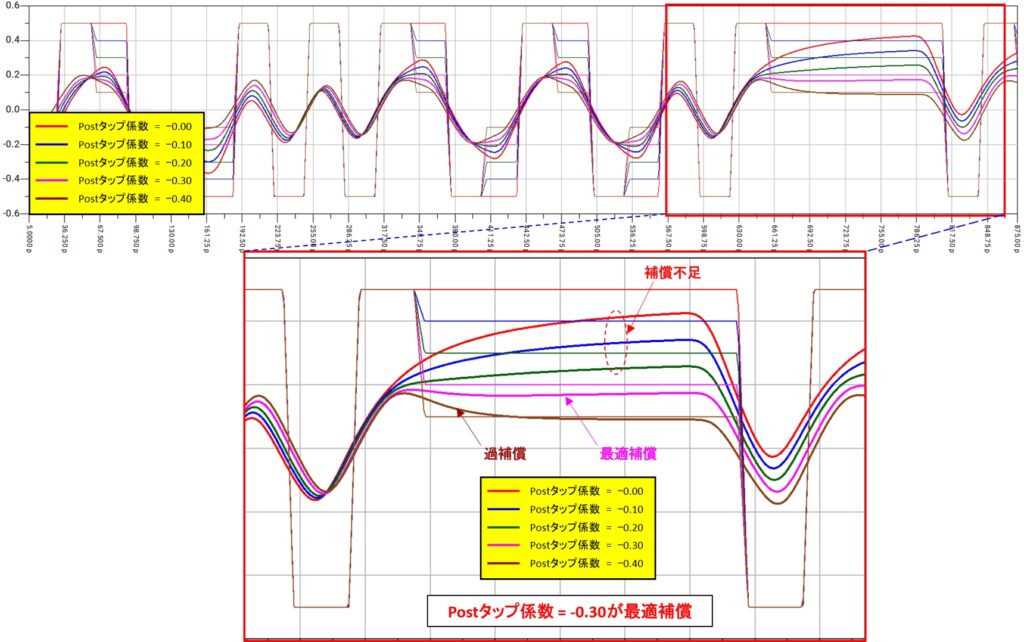

図14は、これら5つの受信端波形を重ねて表示させたものです。

この波形を確認すると、Postタップ係数 = -0.00 (補正無し) (赤色の波形)~Postタップ係数 = -0.20(緑色の波形)までは、立上り波形のエッジ部分が後ろに尾を引いており補償不足であることが確認できますが、Postタップ係数 = -0.30(ピンク色の波形)では、きれいな矩形波となっており、更にPostタップ係数 = -0.40 (茶色の波形)まで増やすと過補償となっている様子が読み取れます。

今回、実験に使用した伝送チャンネルにおいては、PreカーソルよりもPostカーソルの補正の方が、効果が高くなっていました。

このあたりは伝送チャンネルの周波数特性に依存するものと考えています。 今回は、純粋なプリント基板による伝送路のみを使用していますが、実際にはデバイスのパッケージやコネクタによるに損失や反射が混在すると、Preカーソルの効果が高くなることも想定されます。 ただ、前述したとおり、インピーダンス不整合による反射などは、イコライザで調整するものではなく、可能な限りインピーダンス整合を取ることを重視するべきではないかと思います。