技術コラム Column

- si

- 連載コラム :シグナルインテグリティ(SI)改善のポイント

高速シリアル通信とイコライゼーション (3)

前回(第9回)および前々回(第10回)のコラムでは、高速シリアル通信においてイコライザが必要となる背景を説明し、FFE、CTLE、DFE の基本動作と、その効果をシミュレーションにより検証しました。 今回のコラムでは、PCI Express システムを例に、プリント基板配線設計において、特に、イコライザによる補償が困難で不可避的に発生する特性インピーダンスの不連続点に着目し、これら不連続箇所を配線設計の最適化によって改善を行い、アイ開口を拡大した事例を紹介します。

目次

解析対象のシステム構成

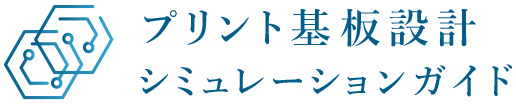

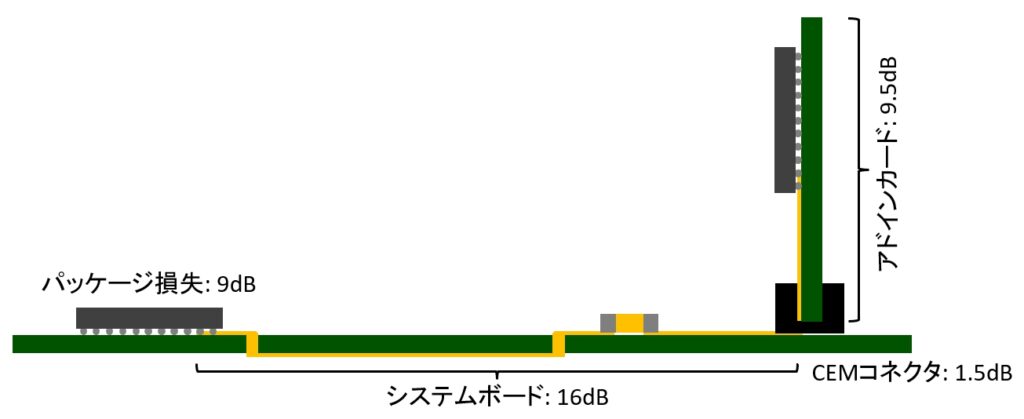

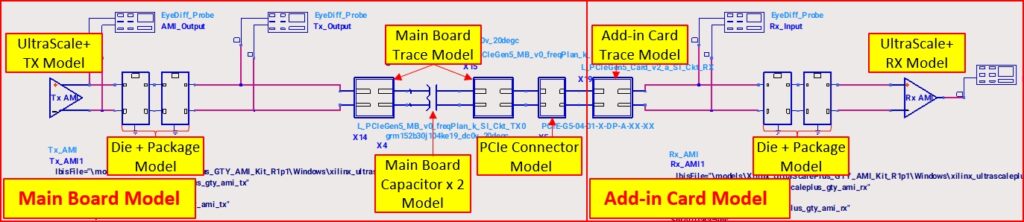

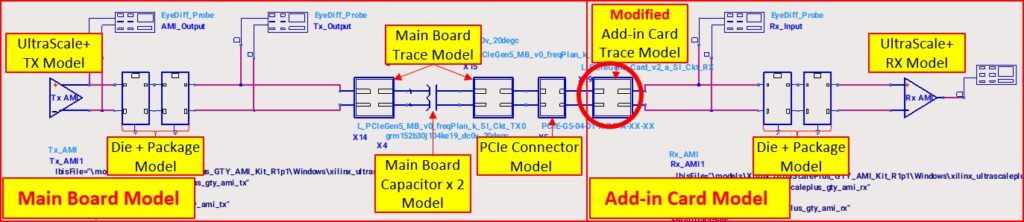

図30は 今回解析対象とするPCI Express システムを示しています。 現実のシステムにおいては、基板配線部において、ICのパッド周辺(特にこの例のように BGA パッケージのパッド部分からの引き出し部)、コンデンサやフィルタのパッド周辺、ビア周辺、コネクタパッド部、カードエッジ部など、多数の特性インピーダンス不連続箇所が存在します。基板配線以外においても、ICデバイスのパッケージ損失やコネクタの挿入損失が加わります。

これらはいずれも、システム的に必ず必要であるにも関わらず、特性インピーダンスを一定値に維持することが難しく、局所的な乱れが生じるポイントとなります。実際の配線設計においては、こうした不連続箇所を可能な限り抑制し、アイ開口への影響を最小限に抑える必要があります。 そして、これら不連続要因は、いずれもイコライザによる補償が困難であるという点に注意が必要です。

本コラムでは、このシステムにおける差動信号のシミュレーションを行い、アイ開口の改善例を示します。

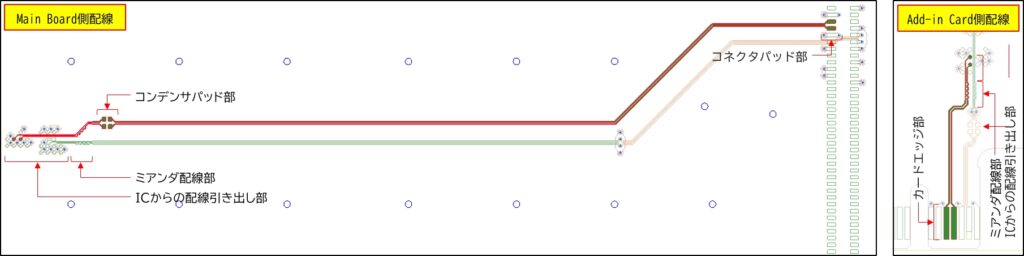

基材は、Main Board、Add-in Cardともに、一般的なFR4基板、8層、差動信号はマイクロストリップラインで構成され、特性インピーダンスは85Ωとなるように配線幅・配線間スペースを取っています。また、Tx-Rx間が等長となるようにミアンダ配線が施されています。

理想配線による限界性能の検証

実配線の解析を行う前に、解析対象となる差動信号と総配線長が同じで、同一の設計ルールを適用し、特性インピーダンスが完全に連続している条件におけるアイ開口がどの程度得られるかを検証し、理論的な限界性能を事前に確認します。

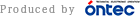

図31は解析する基板と同じ155mm長 (図30のPCI Expressシステム構成の総配線長とほぼ同じ) のマイクロストリップ差動配線で、図32はこの配線のSパラメータ(透過特性と反射特性)を解析した結果です。(赤線が透過特性、青線が反射特性です。) 一例として、PCI Express Gen5 におけるナイキスト周波数(16GHz)での損失を確認すると、約8.5dB でした。

例えば、PCI Express Gen5 におけるチャンネル損失の許容値は図33で示すように合計で 36dB とされています。 この値は配線損失だけでなく、パッケージ損失や CEM コネクタ損失も含まれていますが、これらを除いたとしてもまだ余裕があります。

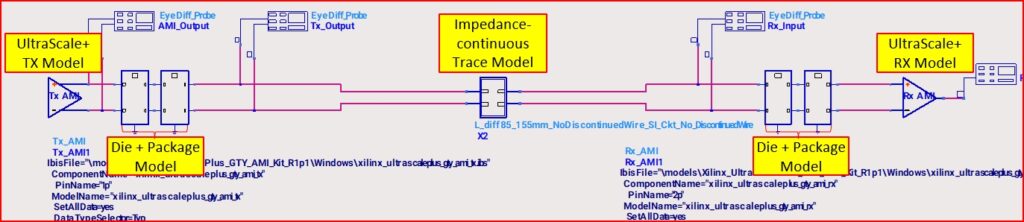

図34は、この不連続ポイントのない配線に対して実施したアイ解析の構成図を示します。 送受信のモデルには、AMD 社の UltraScale+ デバイス 「XCKU11P-2FFVE1517I」 の GTYトランシーバモデル(IBIS-AMI モデル)に加え、 標準ダイモデルおよびパッケージモデルを使用しています。

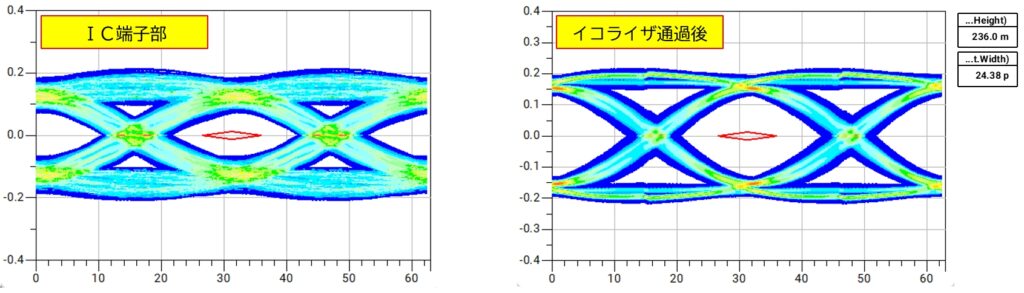

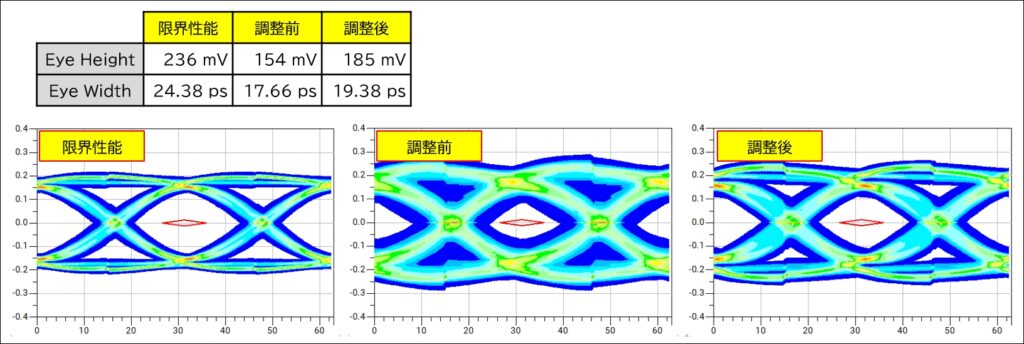

図35にこの構成でのアイ解析結果を示します。なお、本図におけるアイマスク(赤色の菱形)は、PCI Express Gen5 の規定に基づくものです。155mm の特性インピーダンスが連続しているこのチャンネルでは、イコライザ通過後のアイ高さが 236mV、アイ幅が 24.38ps となりました。 これらの結果から、本値が本システムにおける実質的な限界性能であると推測できます。

注意: 本デバイスのGTYトランシーバは、 32.75 Gbpsに対応していますが、公式的には、PCI Express Gen5 規格に対応していません。

実配線での解析(調整前)

続いて、図30で示した実際のPCI Express システムでの解析を行ってみます。

図36は、今回解析に使用したMain Board、Add-in Card、それぞれの配線図です。 Main Boardにおける特性インピーダンスの不連続点として、ICからの配線引き出し部、ミアンダ配線部、ACカップリングコンデンサのパッド部、コネクタパッド部があります。 Add-in Cardにおける特性インピーダンスの不連続点として、ICからの配線引き出し部、ミアンダ配線部、カードエッジ部があります。

図37は、このシステム例で実施したアイ解析の構成図を示します。送信側・受信側には、先ほど同様、AMD 社の UltraScale+ デバイス XCKU11P-2FFVE1517I の GTYトランシーバモデル、標準ダイモデル、およびパッケージモデルを使用しています。また、PCIeコネクタには、Samtec社のPCIE-G5-08-01-X-EM-WT-TRの Sパラメータモデルを使用しています。

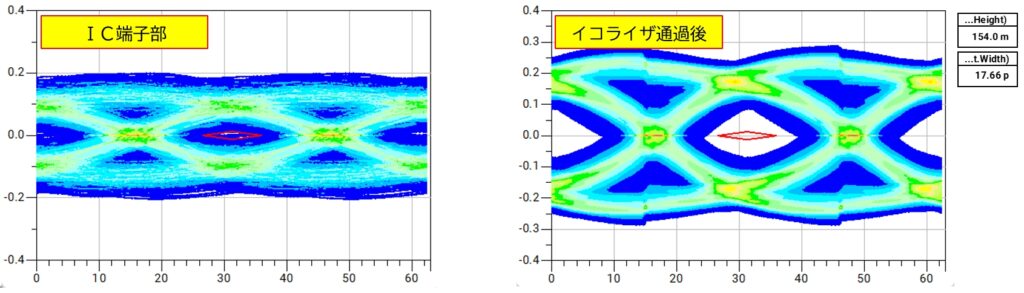

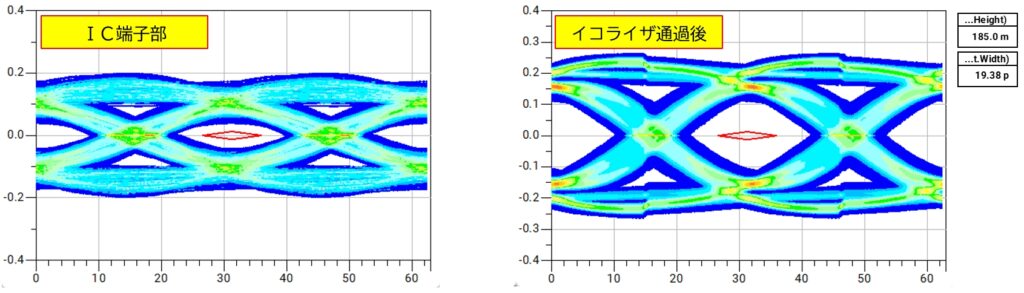

図38にこの構成でのアイ解析結果を示します。本図におけるアイマスクも、先ほど同様、PCI Express Gen5 の規定に基づくものです。 実配線では、不連続点が数多く存在するため、IC端子部でのアイが閉じてしまっています。 イコライザを通過することで、アイ高さが 154mV、アイ幅が 17.66psとなり、規格を満足しているものの、先ほどのアイ開口と比べると、大幅に悪化しているのがわかります。

実配線の最適化

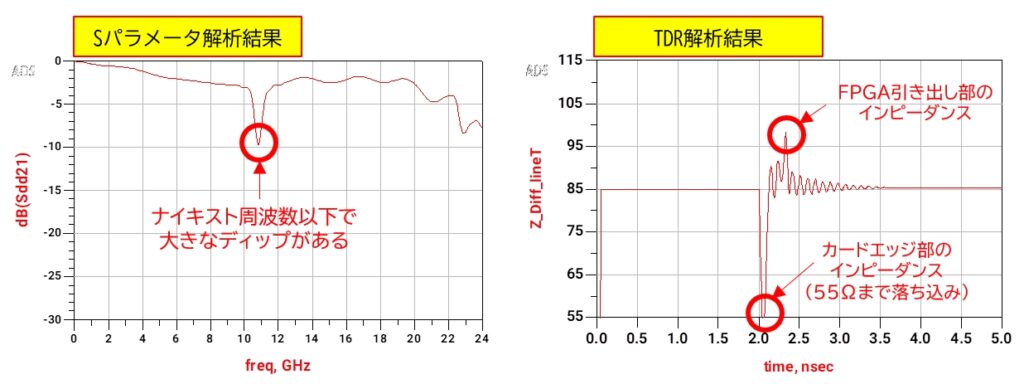

図39に、Add-in Card に対して実施したSパラメータ解析(挿入損失:左図)およびTDR解析※1(右図)の結果を示します。

挿入損失ではナイキスト周波数以下である11GHz付近に大きなディップが発生しており、TDR解析ではカードエッジ部のインピーダンスが55Ω程度まで大きく下がっているのが確認出来ます。

※1 TDR解析(Time Domain Reflectometry)は、配線や伝送線路のインピーダンス不連続性を時間領域で調べる解析手法です。高速な立ち上がりを持つ電圧ステップを配線に印加すると、インピーダンスが変化する箇所で信号の一部が反射します。この反射波の大きさと到達時間を観測することで、どの位置でどの程度インピーダンスが変化しているかを特定することができるというもので、配線の品質評価や不連続箇所の特定に用いられます。TDR解析については、また別の機会に詳しく取り上げたいと思います。

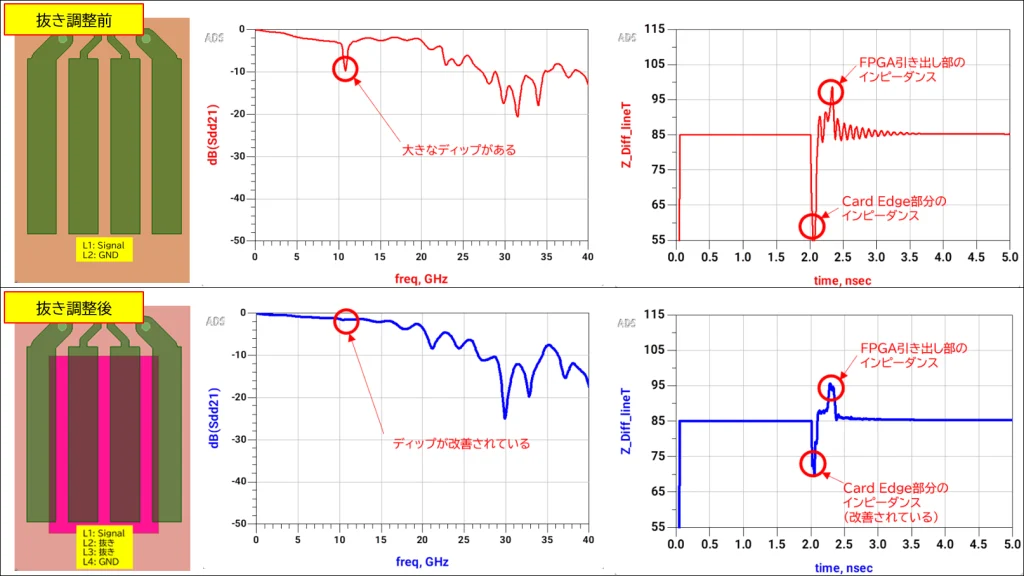

図40は、Add-in Cardのカードエッジ部分の内層プレーン抜き調整を行い、特性インピーダンスの最適化を行った結果です。上段が調整前、下段が調整後で、左から配線図、Sパラメータ(透過特性)解析結果、TDR解析結果となっています。

抜き幅が狭い場合はインピーダンスの改善量が小さく、一方で過度に広げても改善効果は頭打ちとなるため、本設計では適切な広さに設定しています。今回のケースでは、L2 および L3 の 2 層を抜くことで、インピーダンスは約 75 Ωまで改善しています。本事例では 8 層基板構成であり、はんだ面側にも同様の高速信号配線が存在します。そのため、これ以上の抜き層数を増やすことが出来ず、抜きは 2 層が実用上の限界と判断しました。

実配線での解析(調整後)

続いて、内層プレーン抜き調整済みの基板モデルを使用して、アイ解析を行います。 図41にその構成図を、図42にこの構成でのアイ解析結果を示します。 IC端子部でのアイの開口が確認でき、イコライザ通過後でアイ高さが 185mV、アイ幅が 19.38psとなり、抜き調整前の基板モデルと比較すると、大幅に改善しているのがわかります。

まとめ

一連のシミュレーション結果を図43にまとめておきます。

最後に

今回のコラムでは、現実のシステムや基板配線において、局所的に特性インピーダンスが不連続となる箇所を特定し、アイ開口を改善する事例を示しました。 カードエッジ部の抜き調整のみで、アイの開口に大きな差が生じることがご理解いただけたかと思います。

イコライザは高周波損失や符号間干渉の補償には有効である一方、特性インピーダンス不連続に起因する反射の抑制効果は限定的です。 基板設計においては、特性インピーダンスを規定値に制御するために配線幅・配線間スペースを調整し、差動信号のスキューを抑える目的で等長配線を行います。 しかし、実配線では特性インピーダンスが不連続となる箇所の発生を完全に避けることはできません。 こうした不連続箇所については、シミュレーション技術を用いて最適化を行い、限界性能に近づけることで、規格適合や設計マージンの確保に寄与できるものと考えています。